Atig

## Communication Protocols Analysis

Verification of Dynamic Register Automata

Verification of a class of protocols:

- Dynamic creation of processes

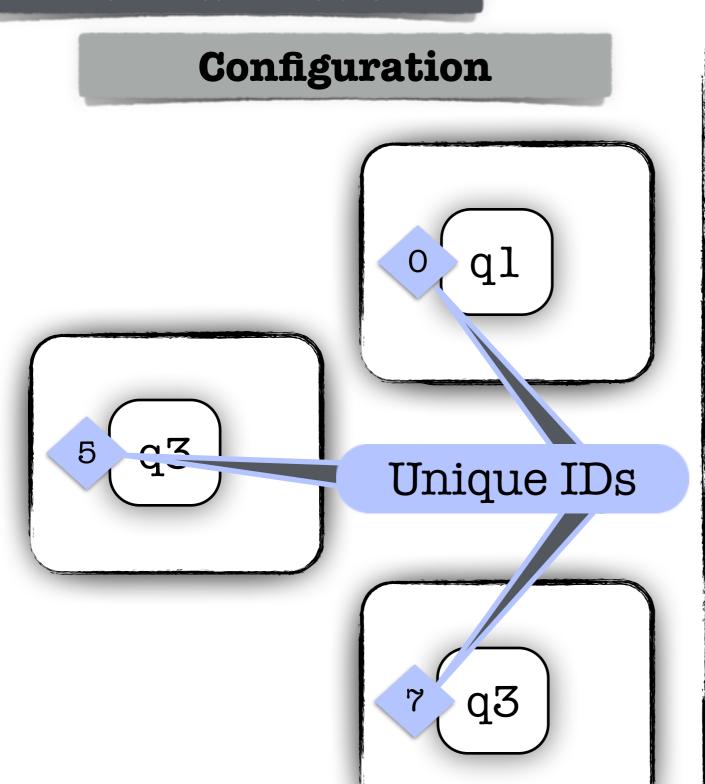

- ▶ **Unique** ID for each process

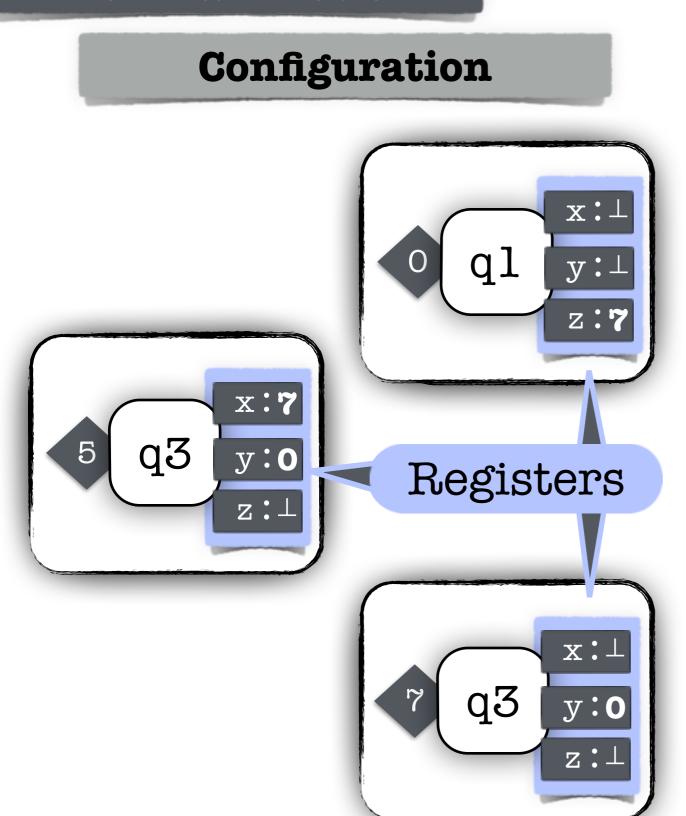

- Finite number of **registers** per process

- Used to store the ID of others

- Point-to-point communication

- **Rendez-vous** communication

Verification of Dynamic Register Automata

[Bollig et al. 2010, 2013]

Verification of Dynamic Register Automata

### **Applications**

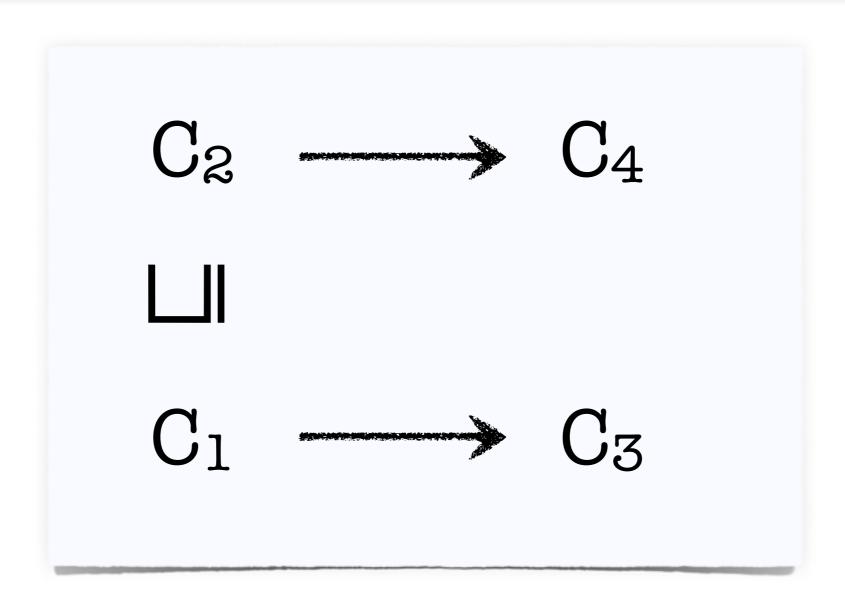

- Leader Election Protocol

- Peer To Peer Protocol

- Ad-Hoc Networks

Verification of Dynamic Register Automata

**Applications**

Formal Model

Verification of Dynamic Register Automata

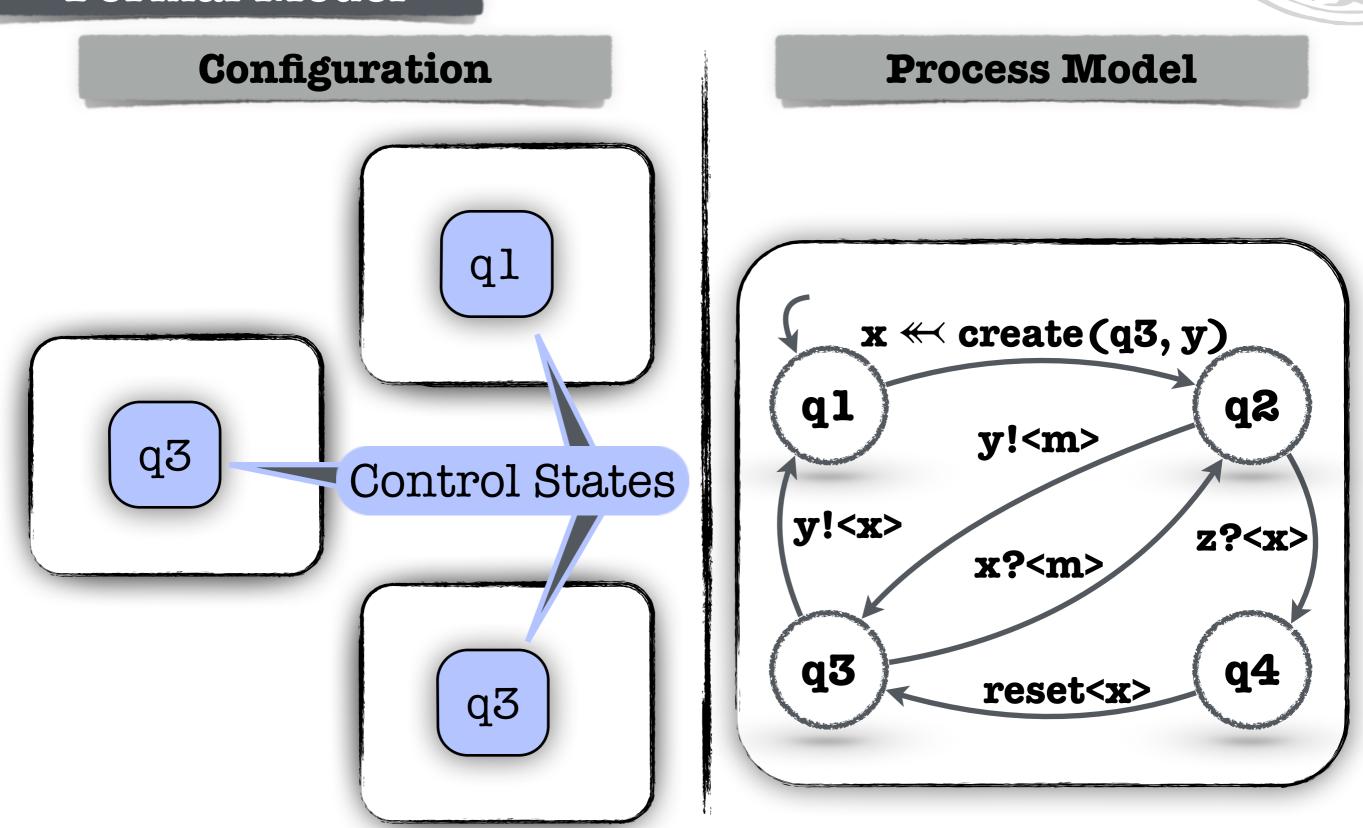

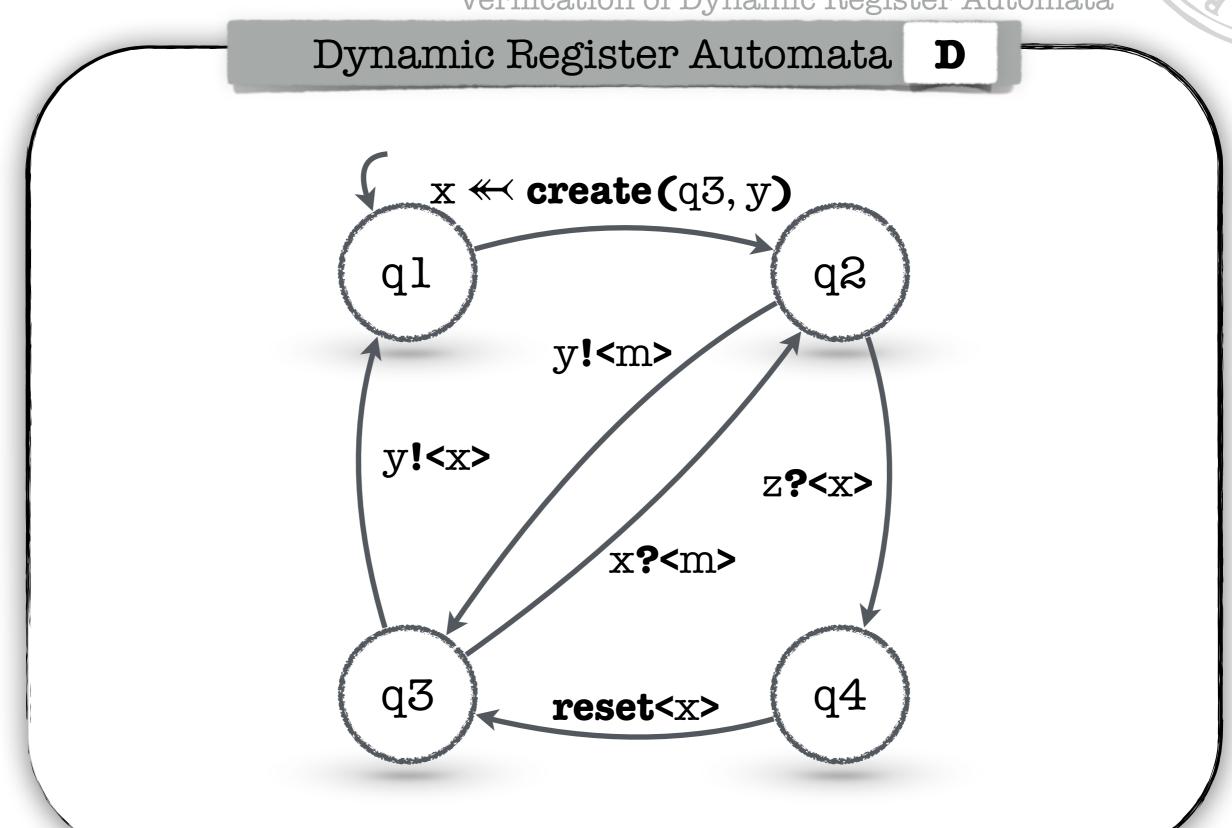

### Formal Model

Verification of Dynamic Register Automata

Formal Model

Verification of Dynamic Register Automata

### Formal Model

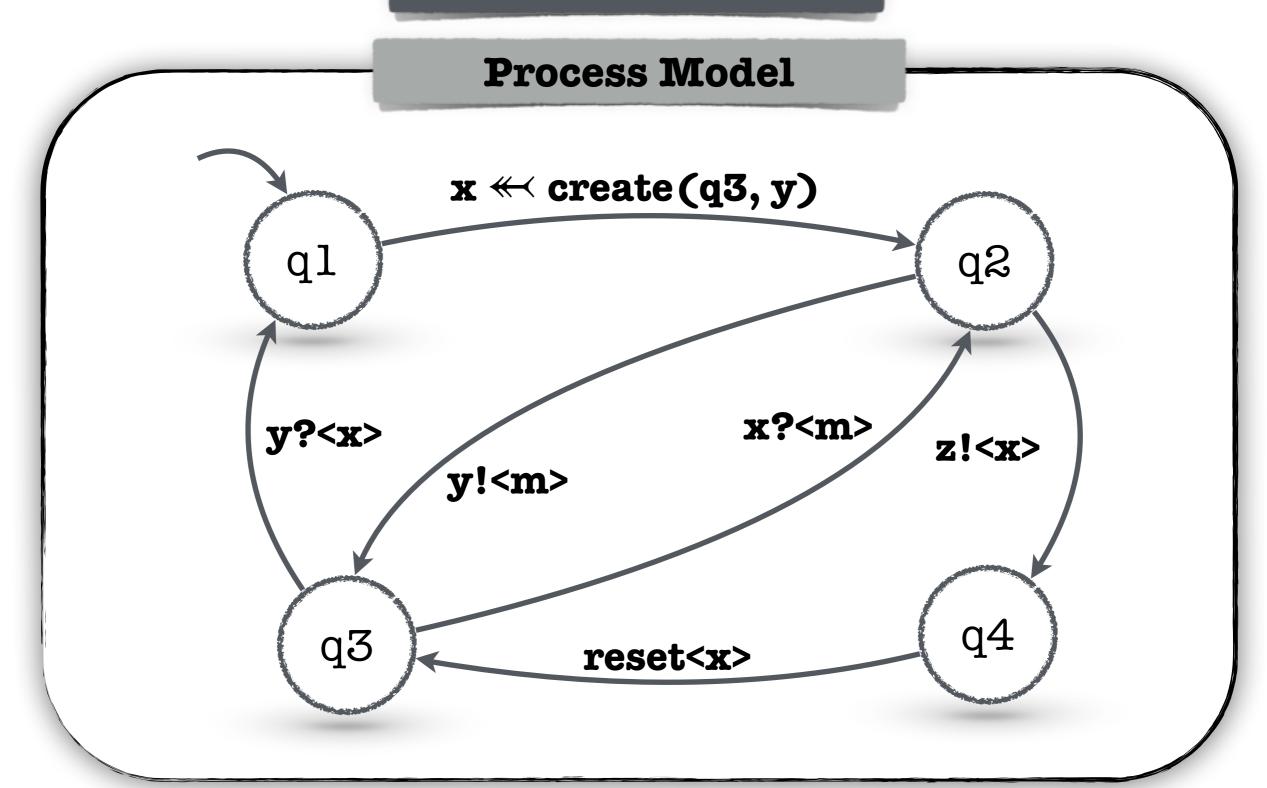

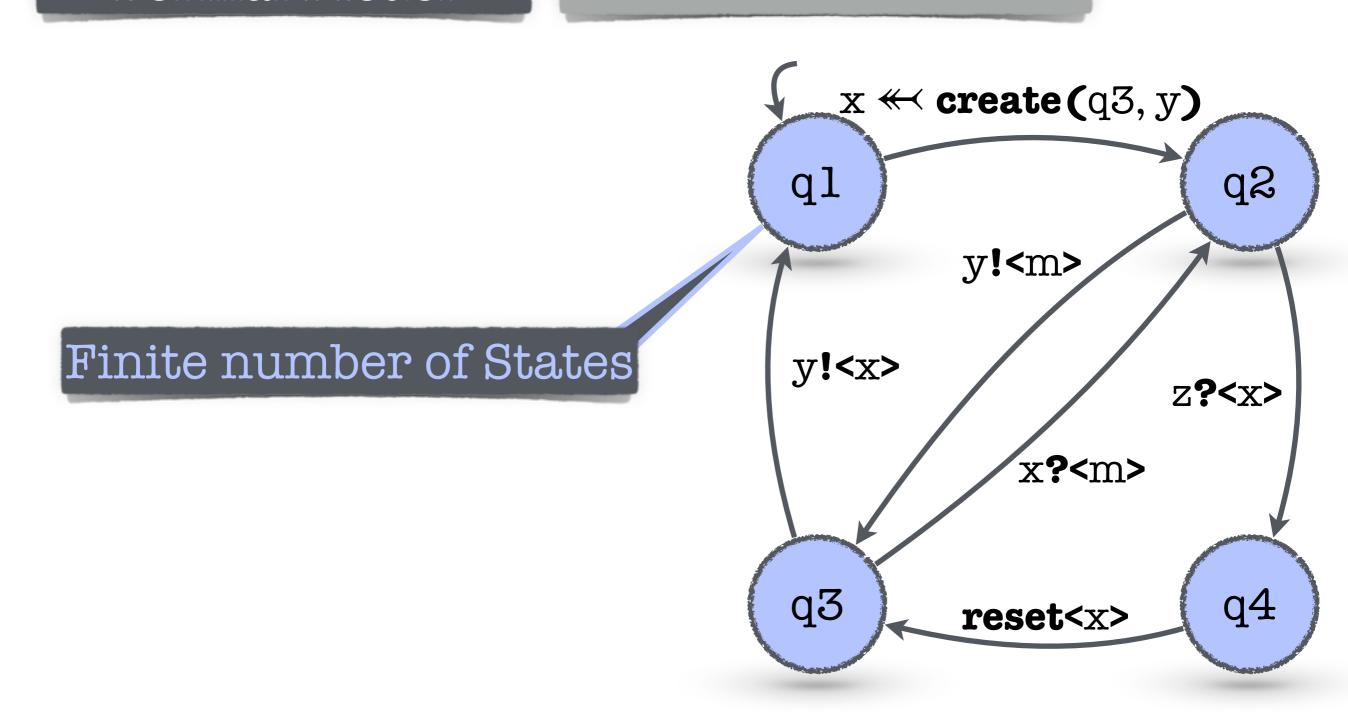

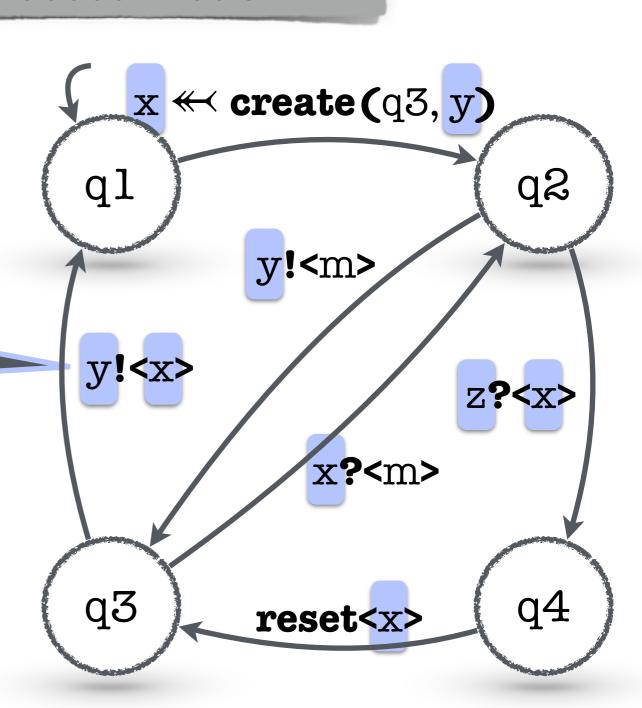

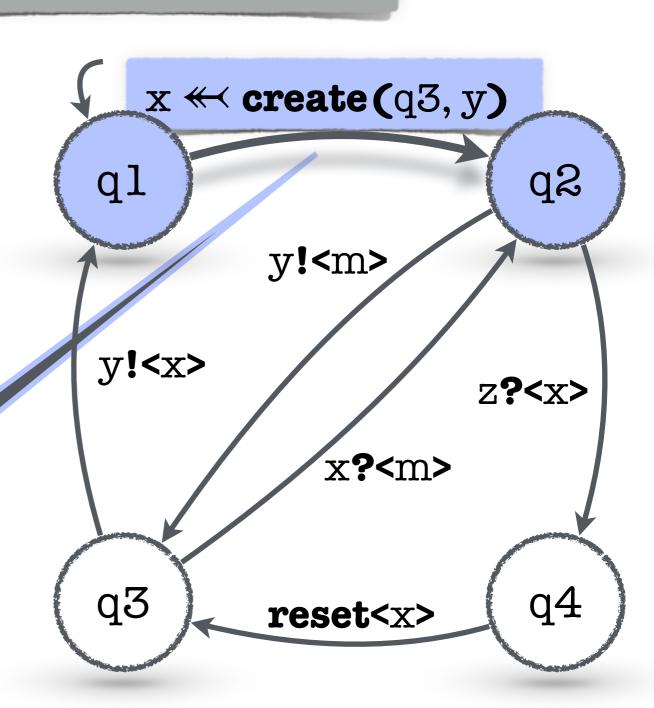

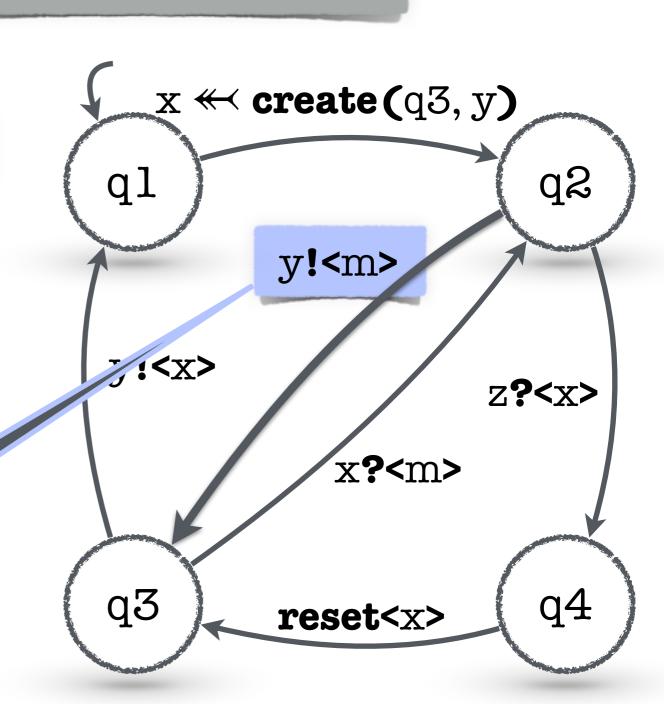

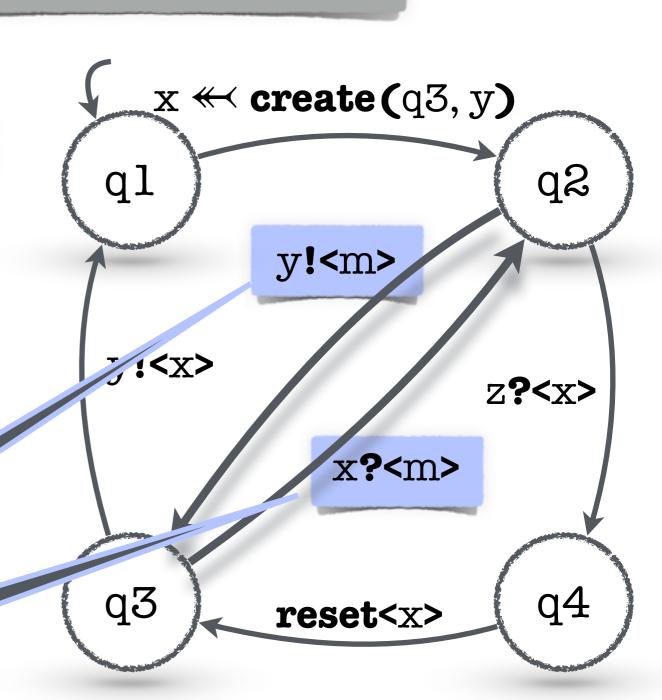

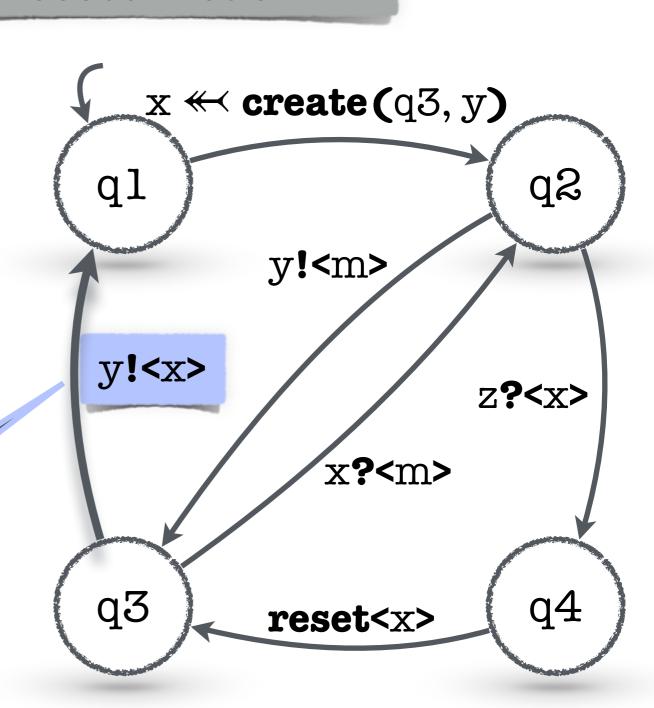

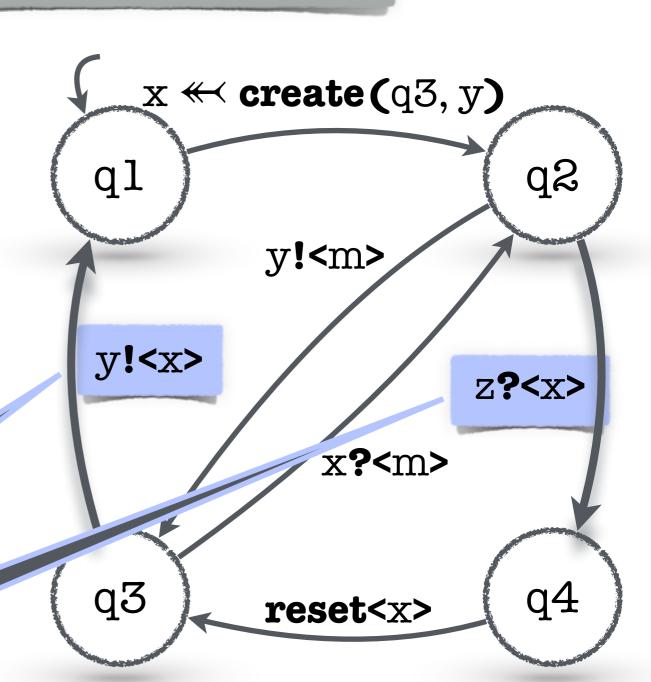

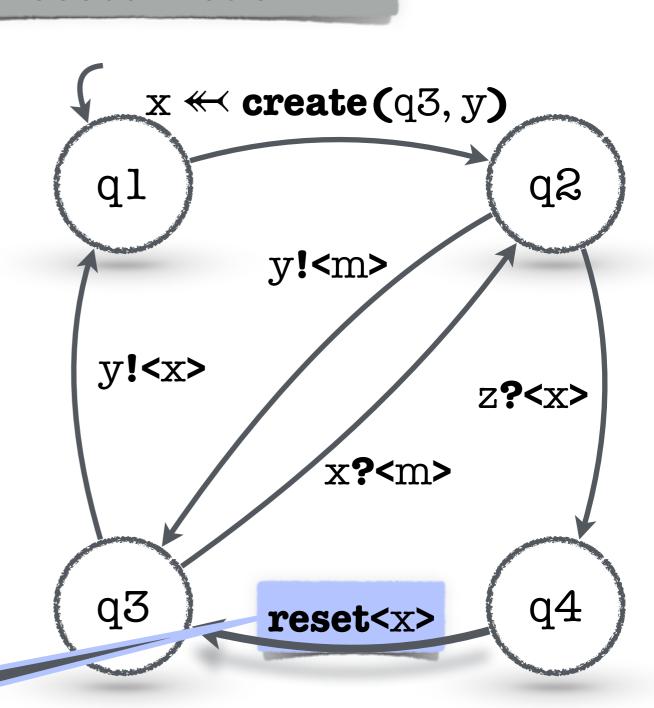

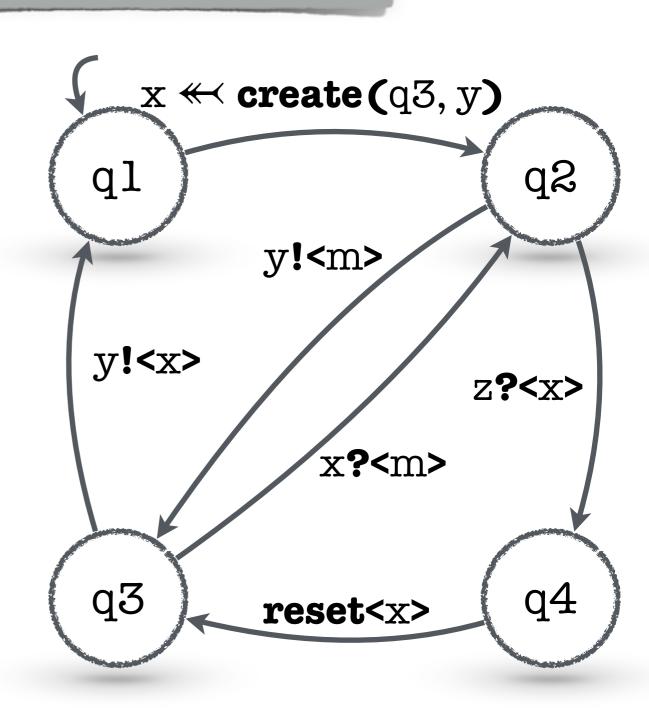

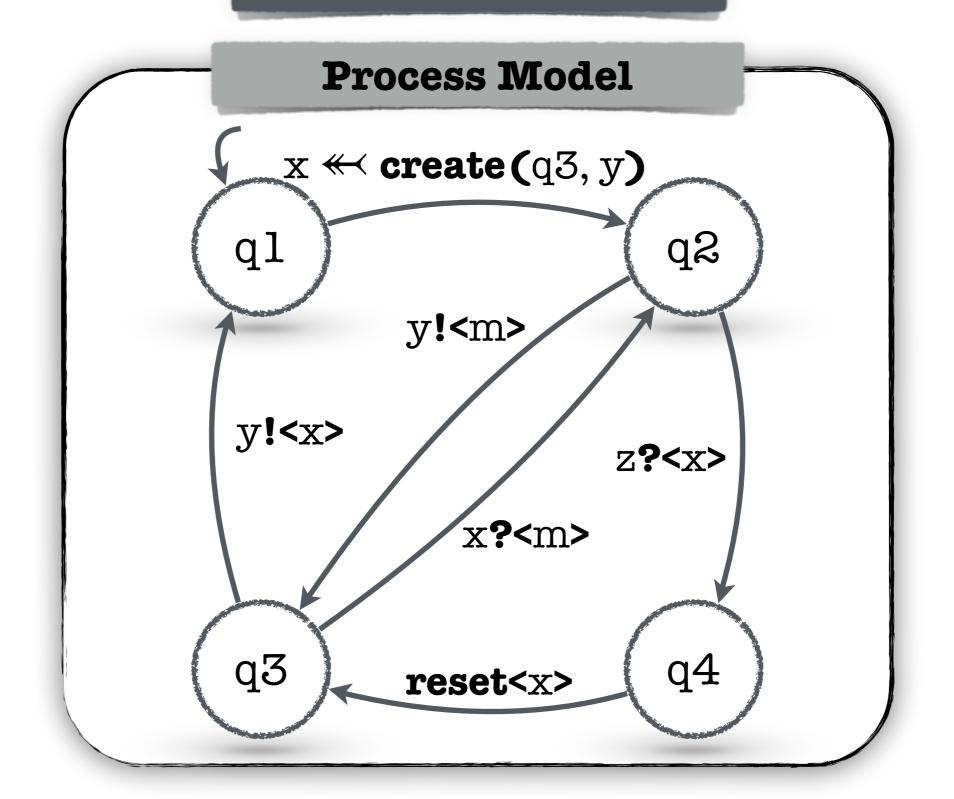

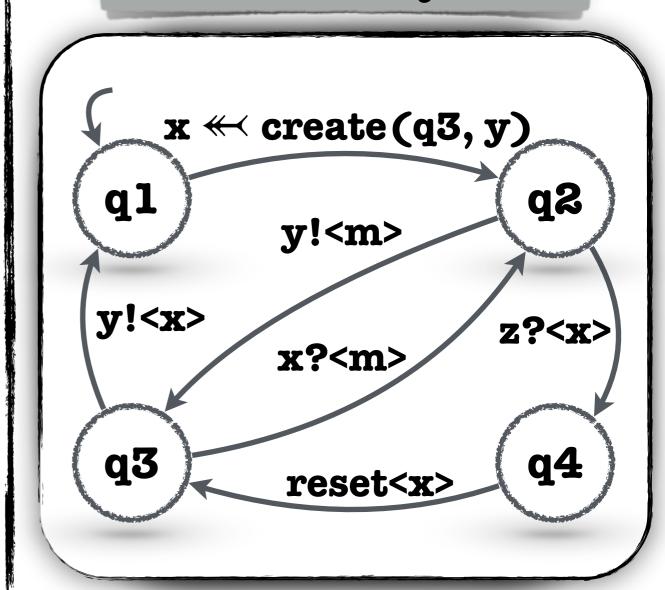

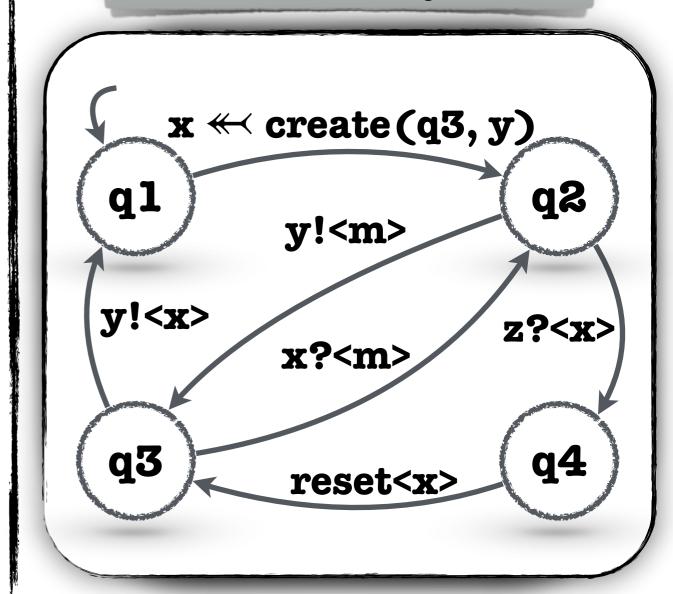

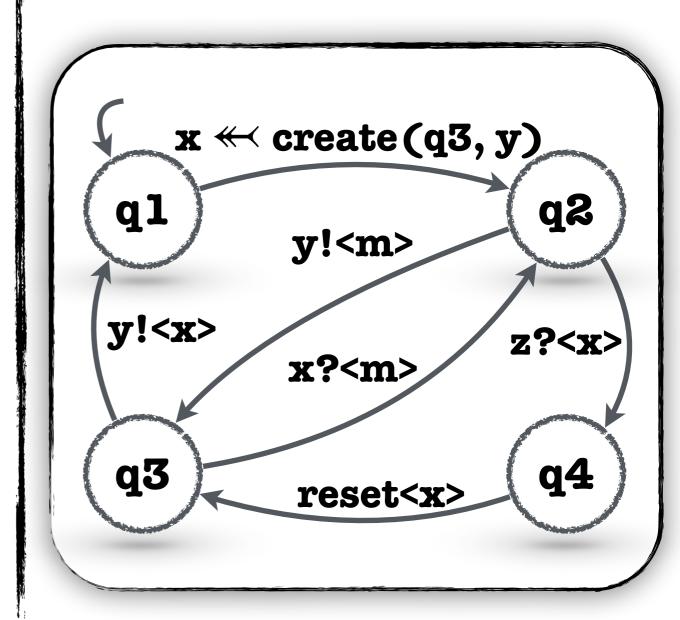

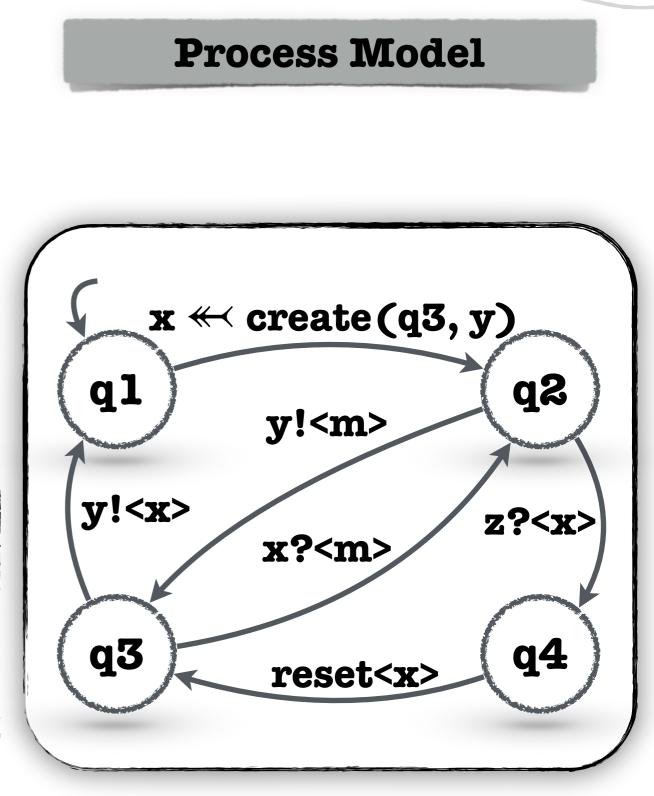

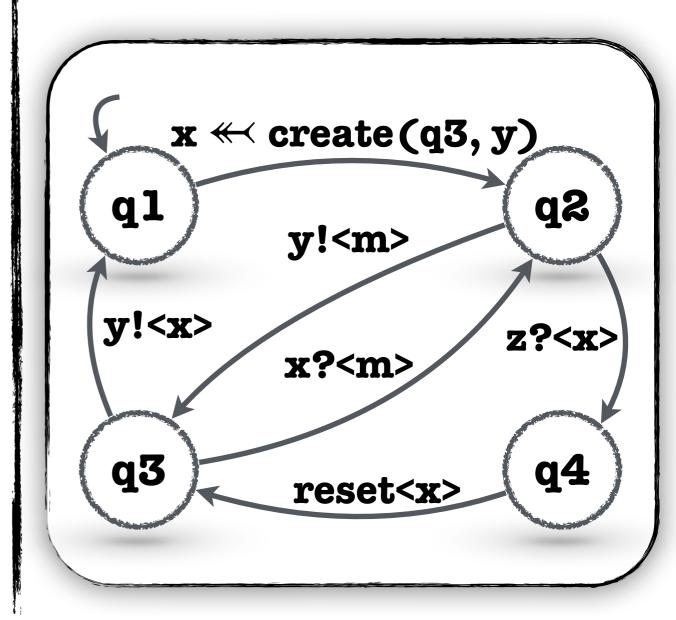

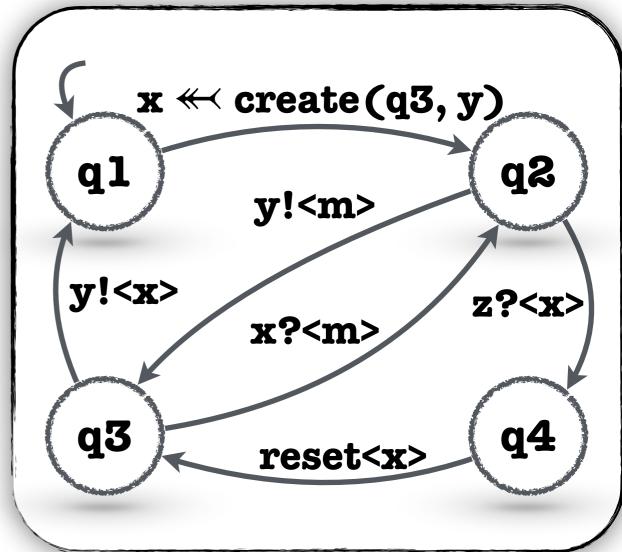

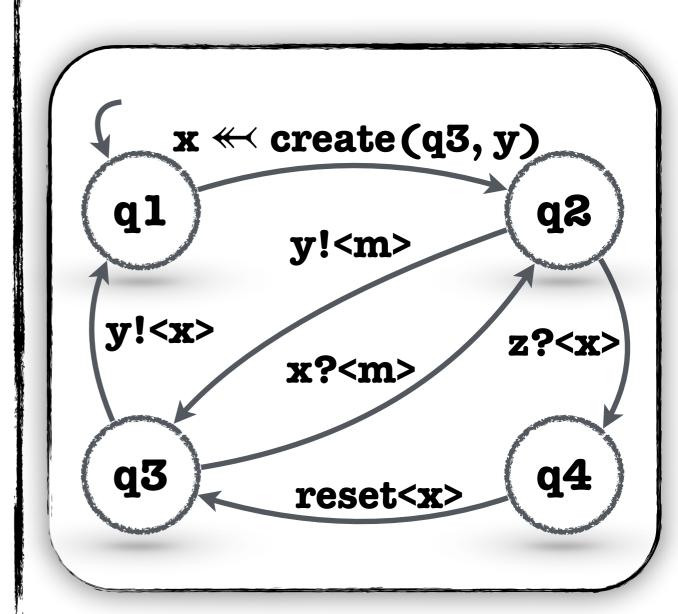

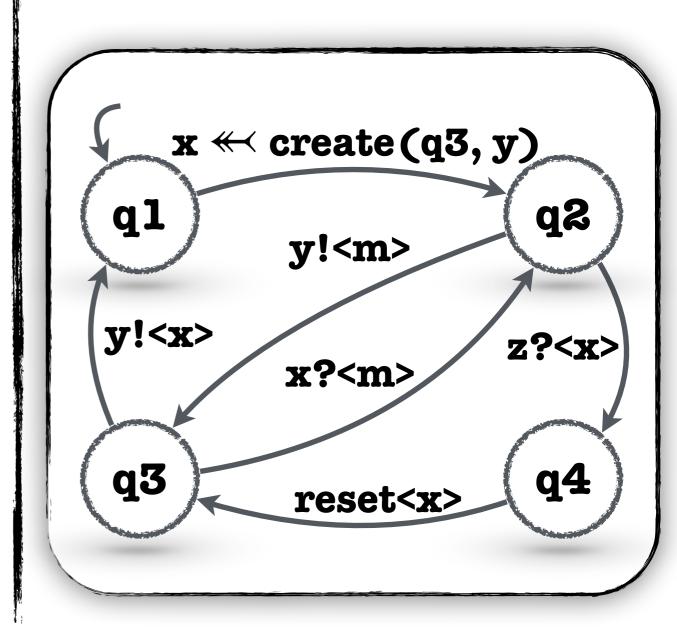

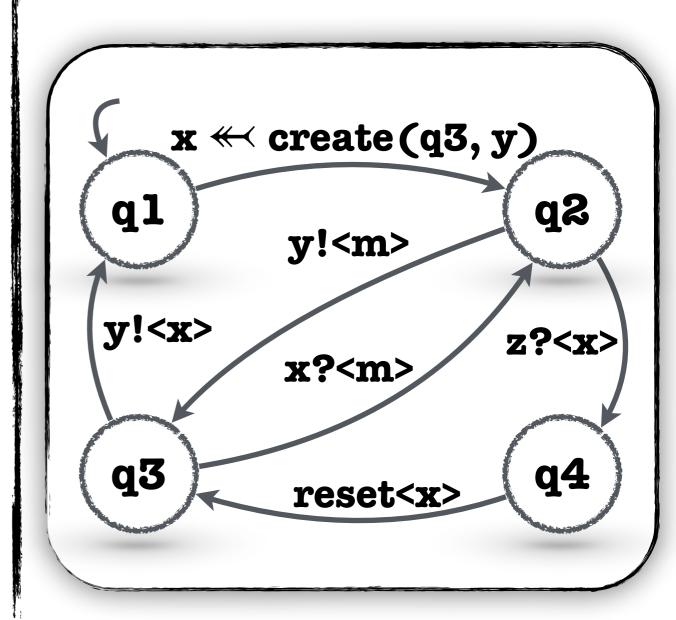

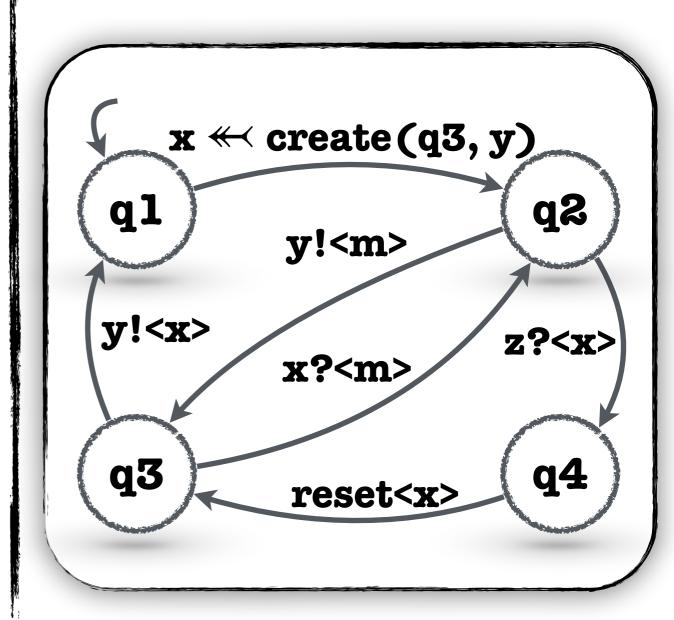

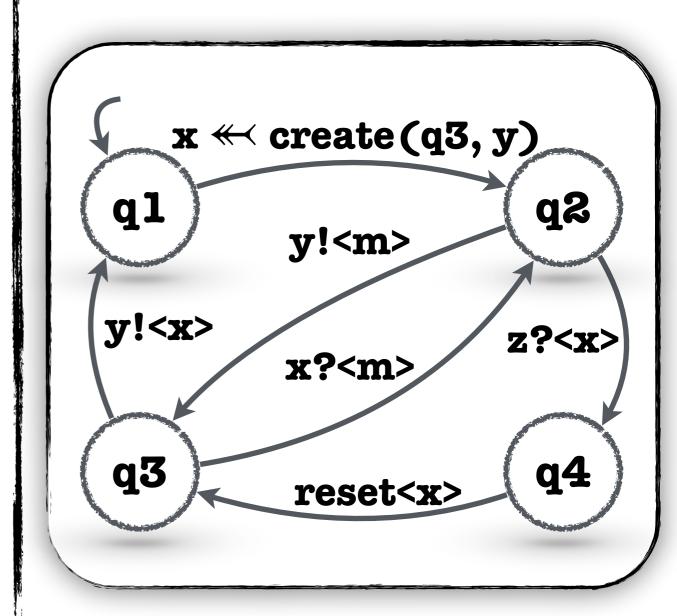

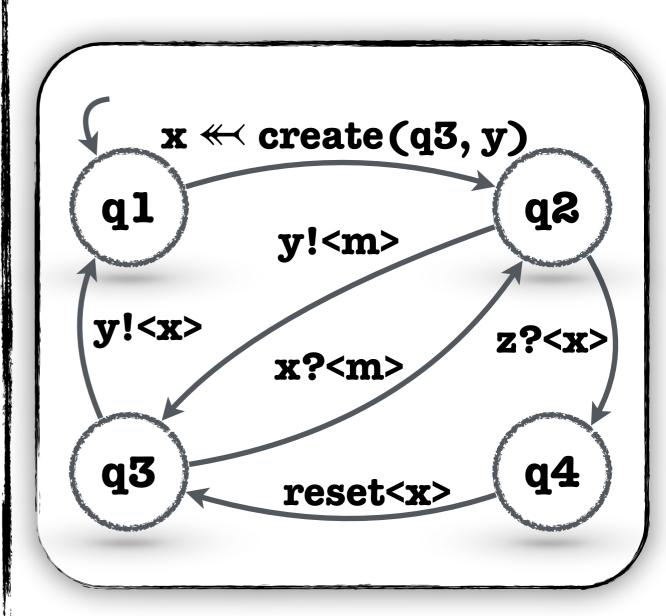

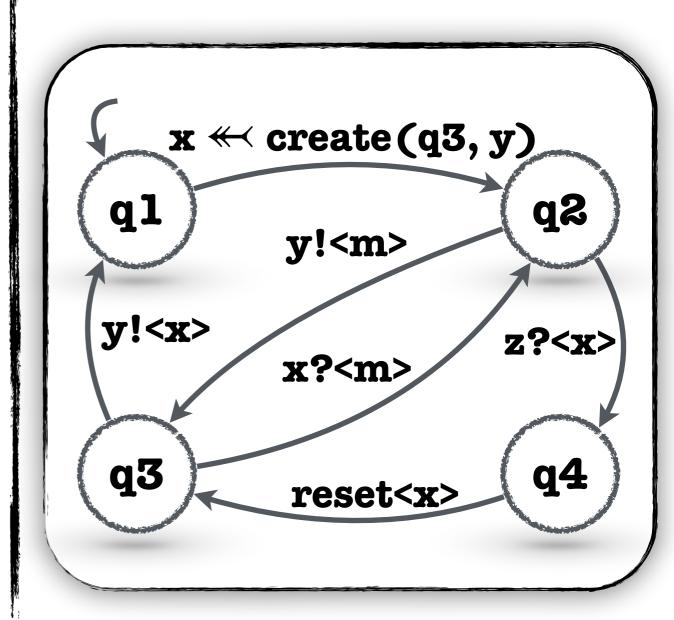

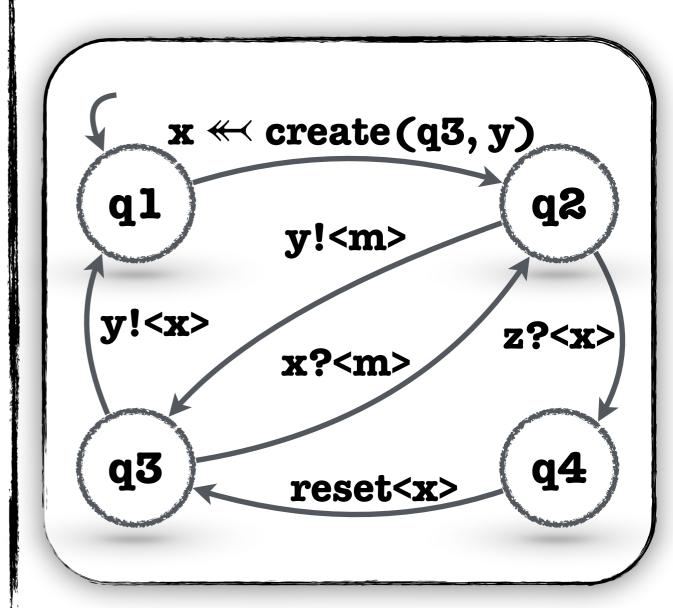

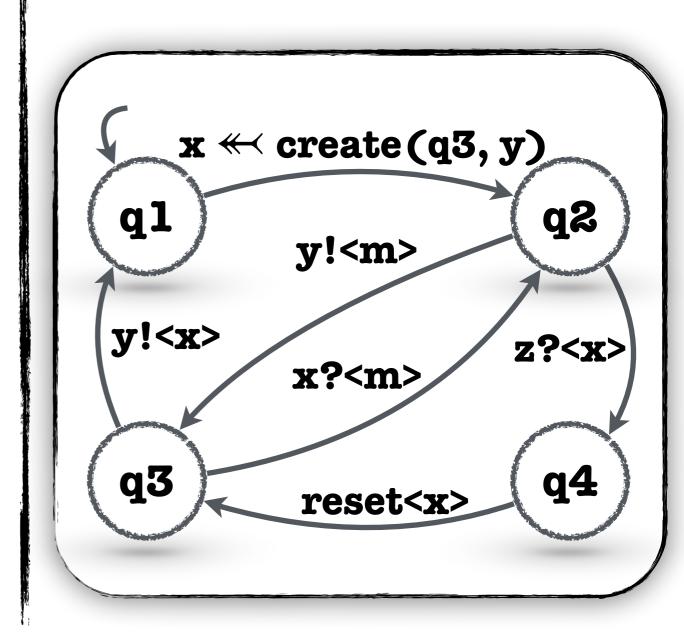

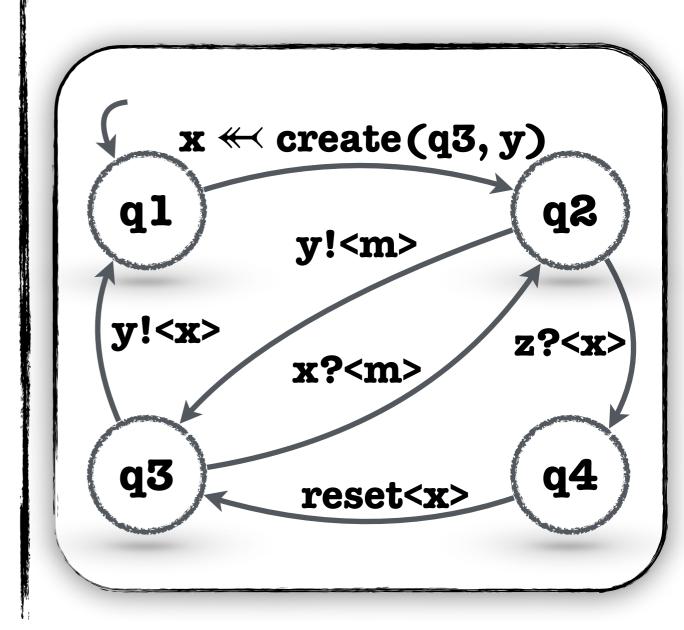

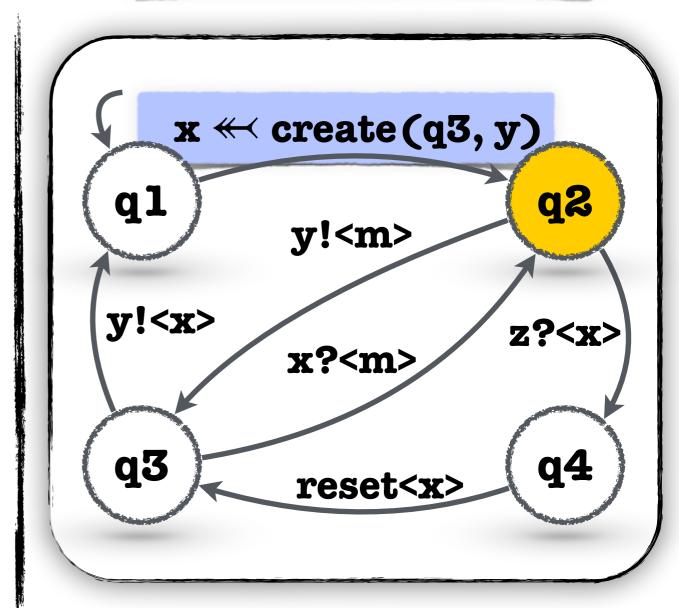

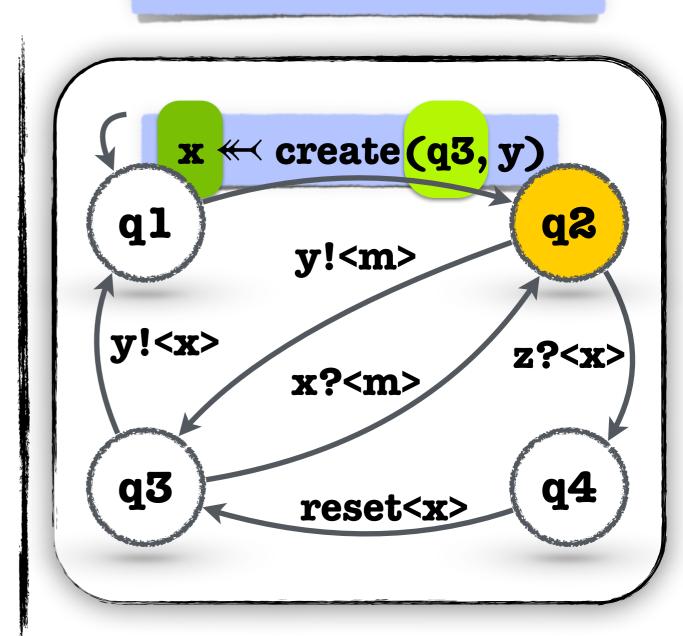

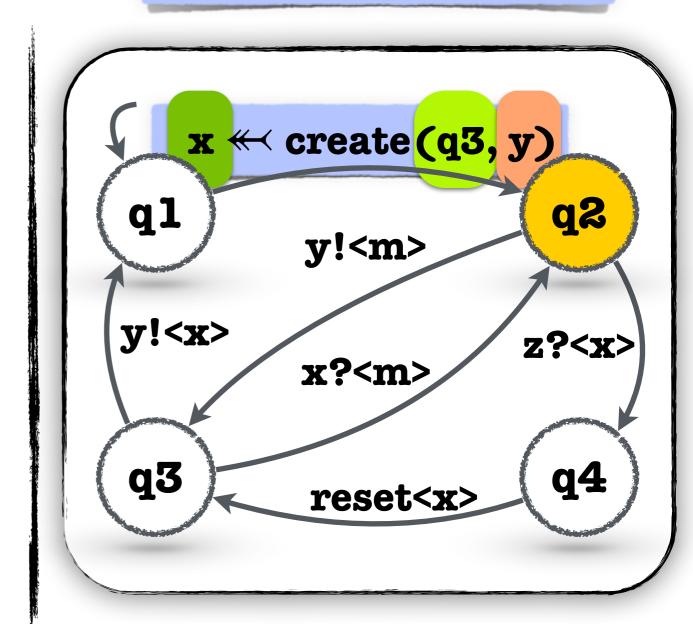

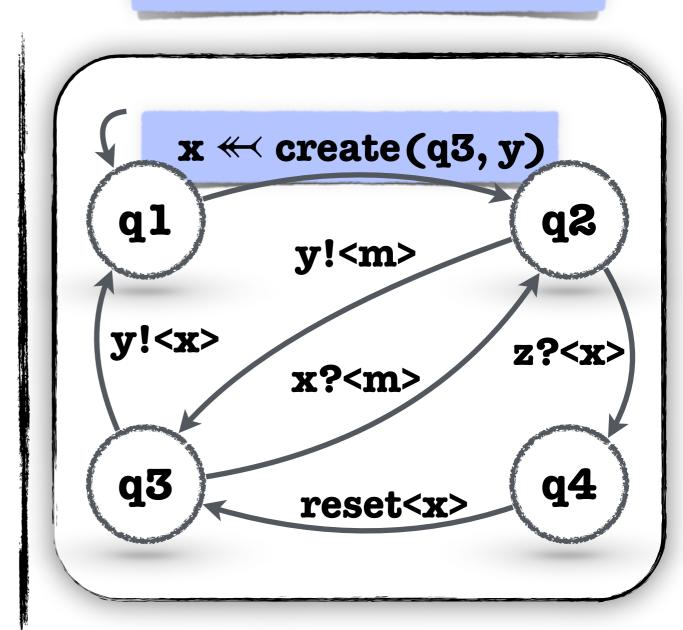

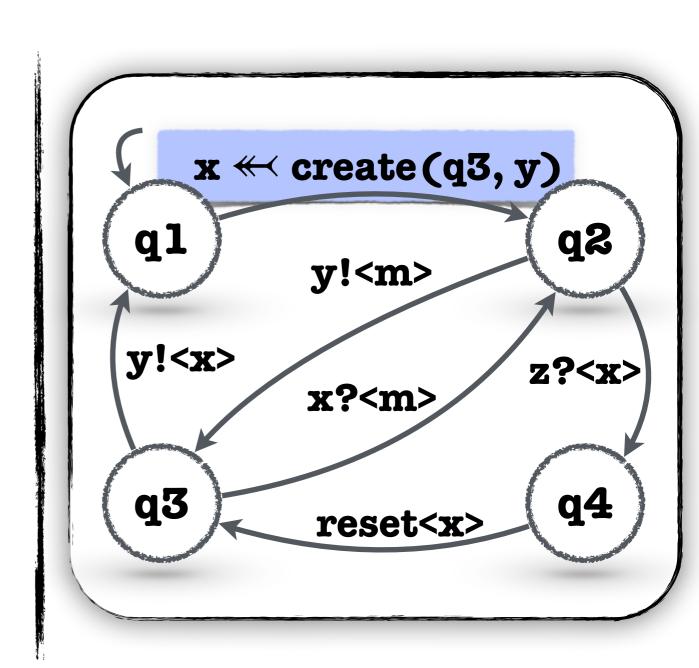

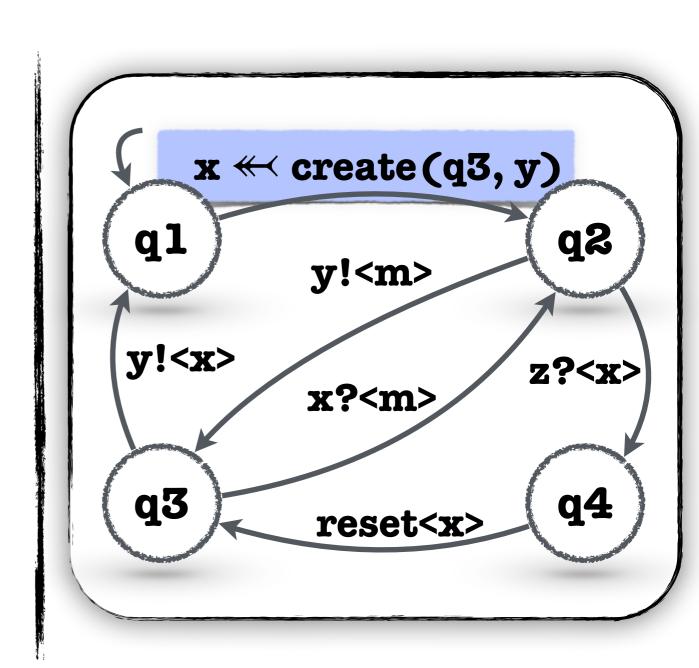

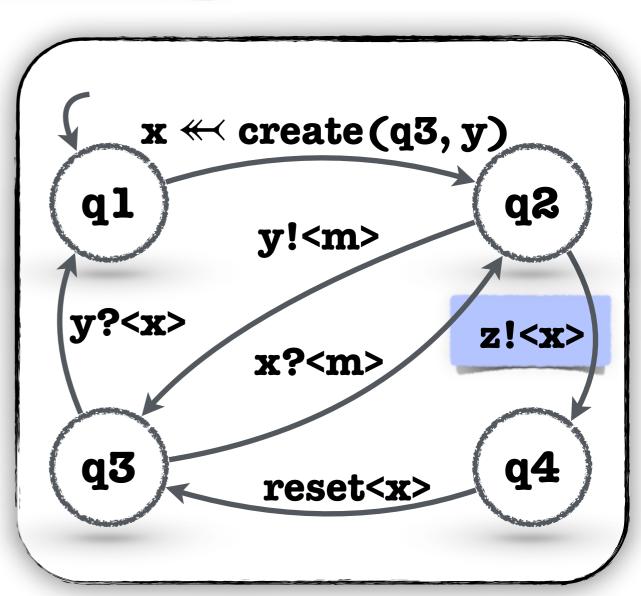

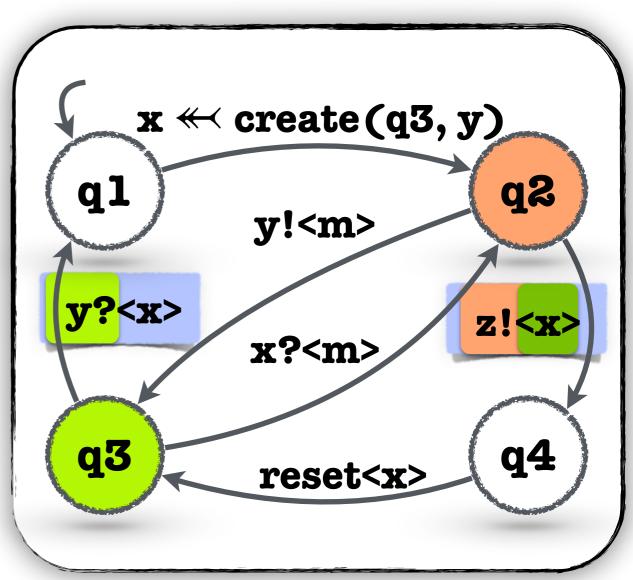

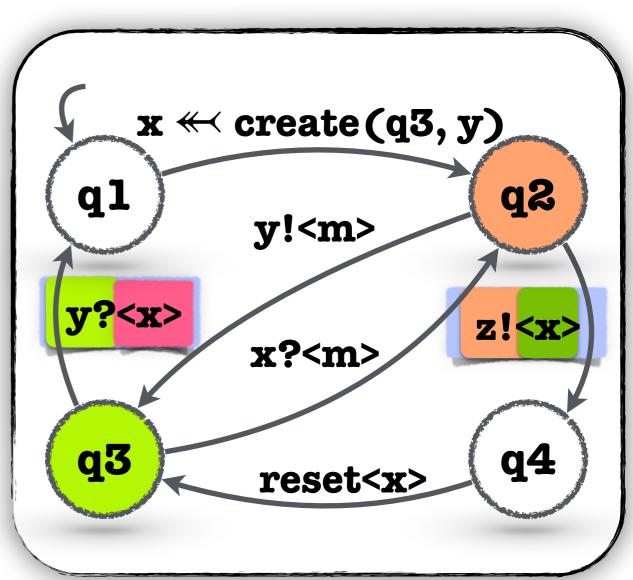

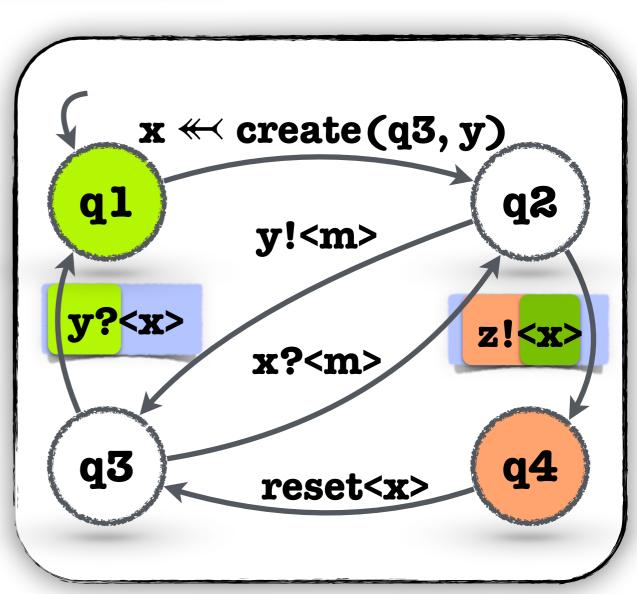

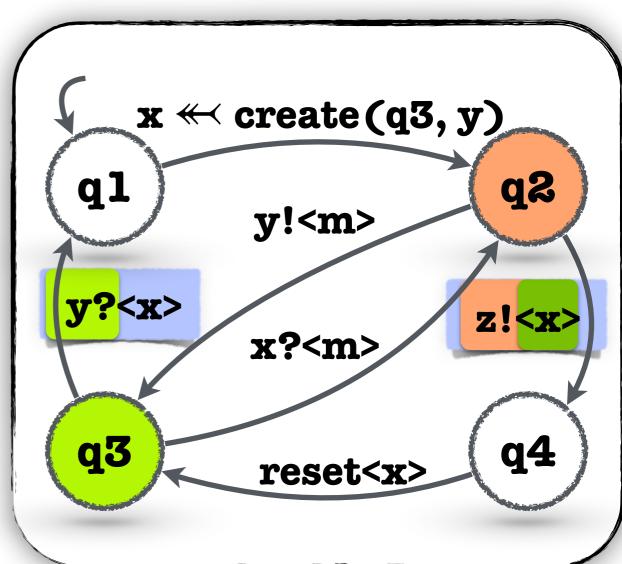

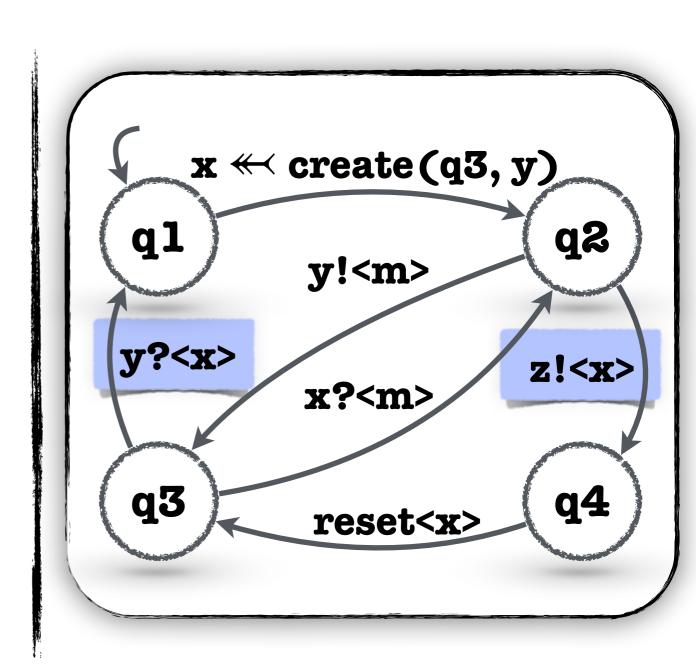

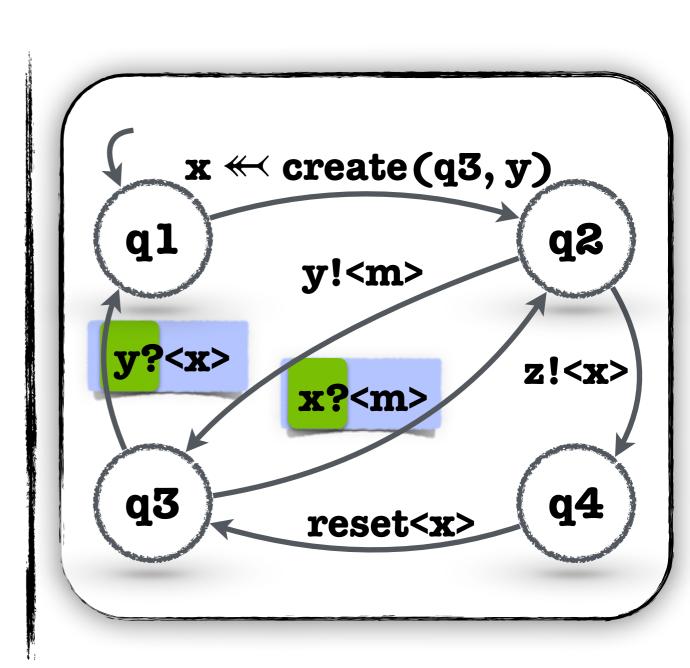

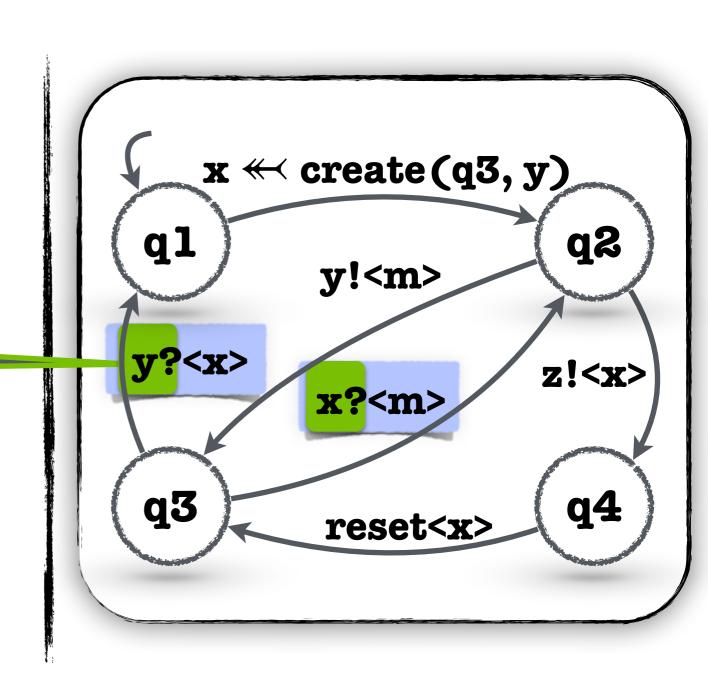

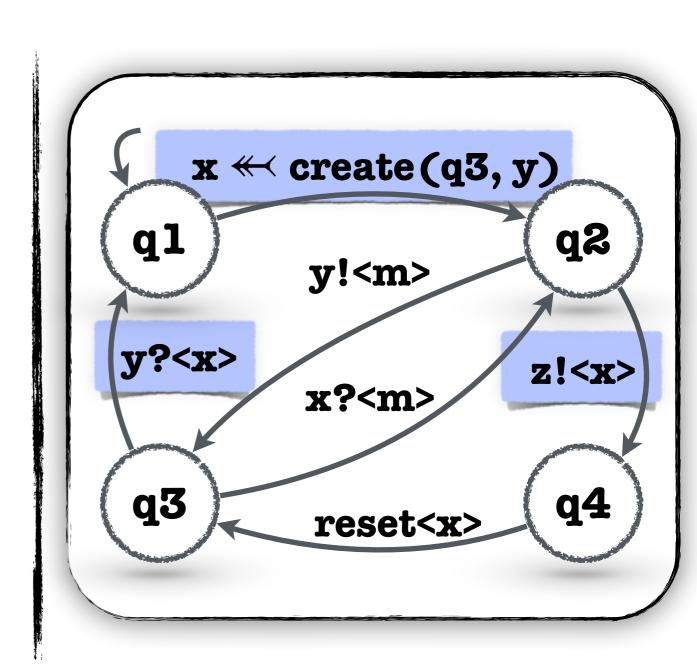

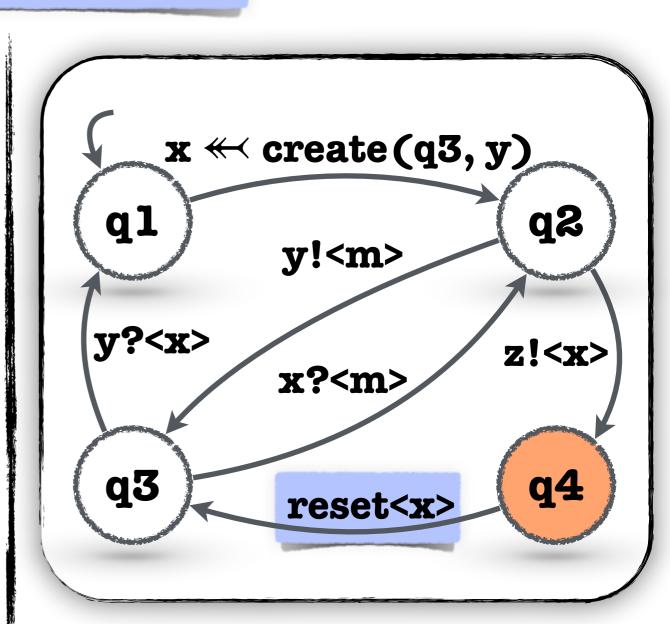

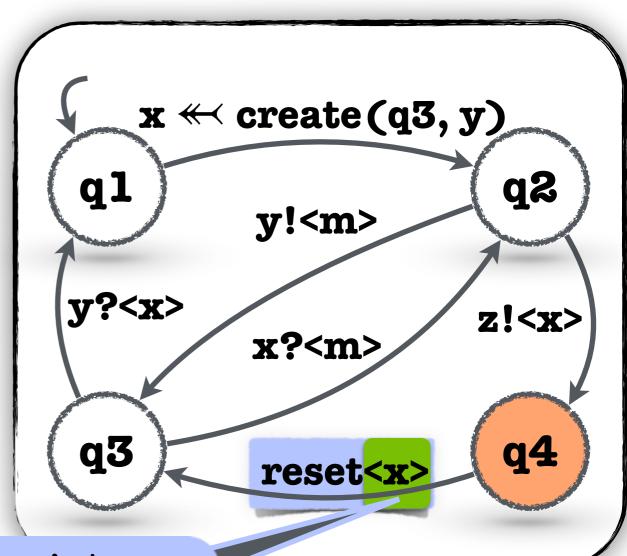

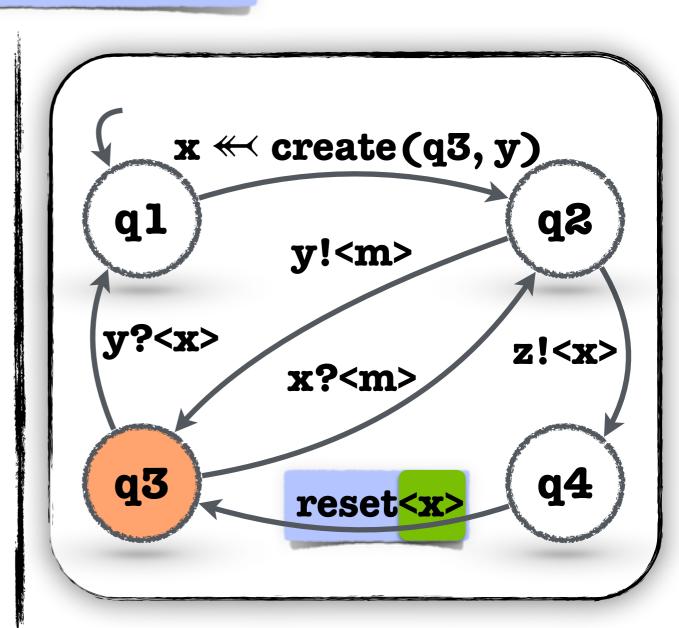

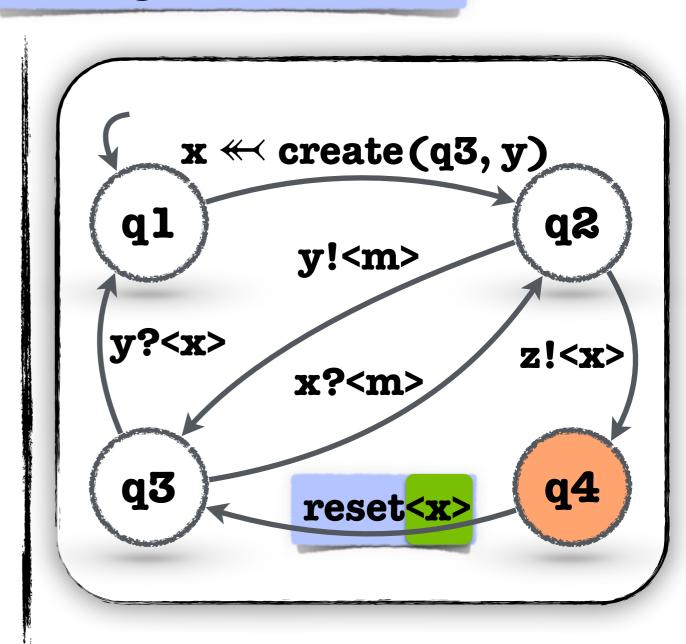

#### **Process Model**

Finite number of States

Finite number of Registers

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

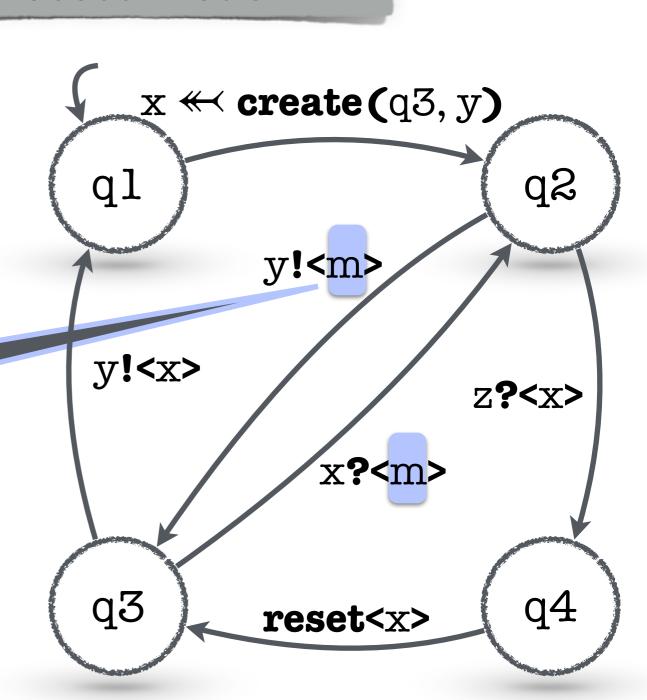

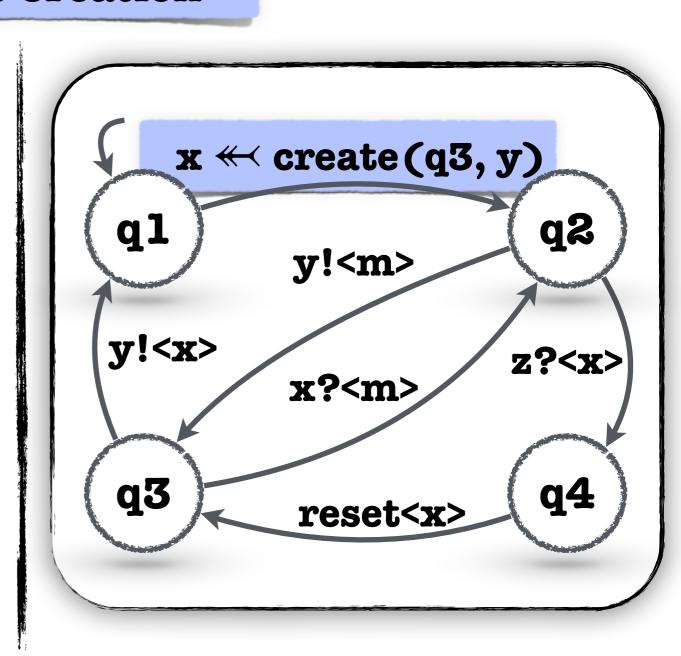

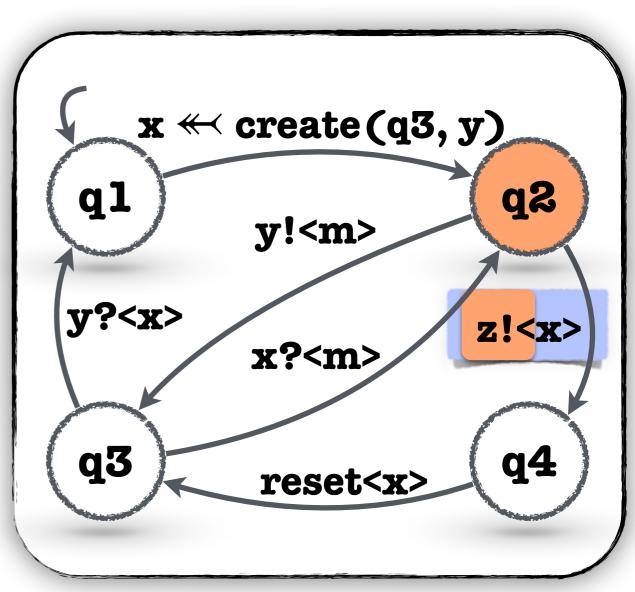

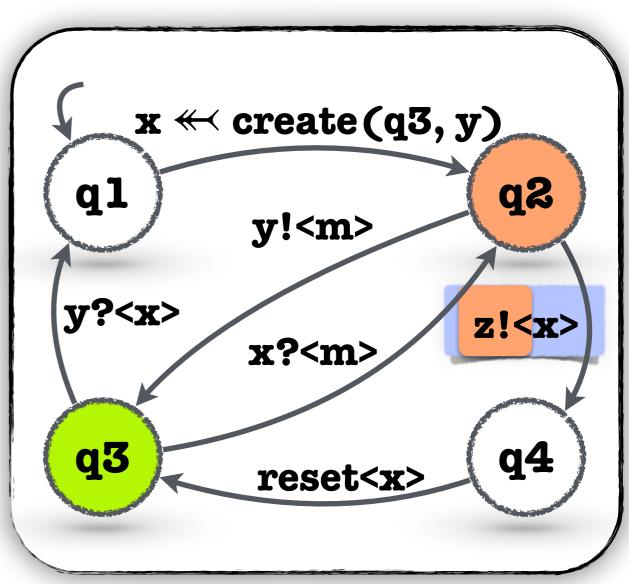

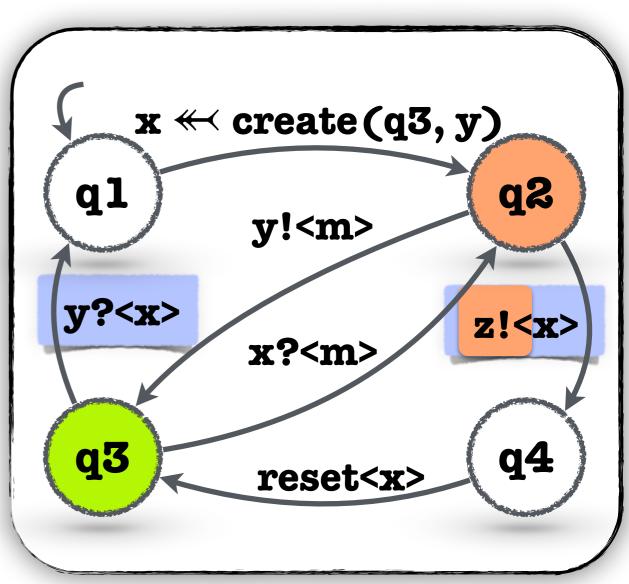

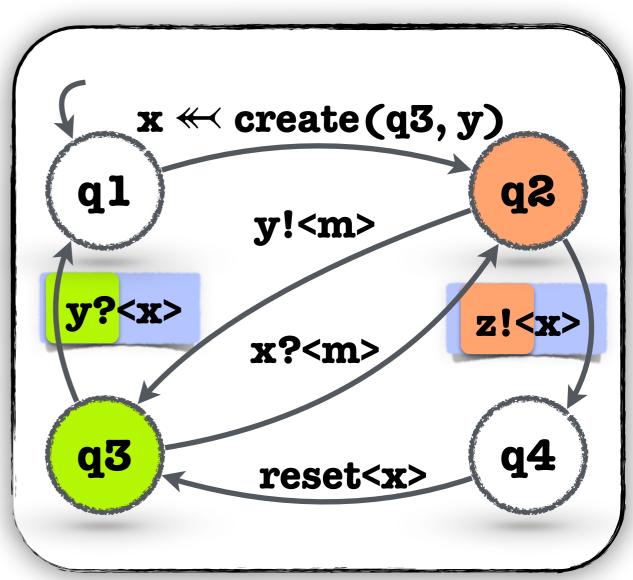

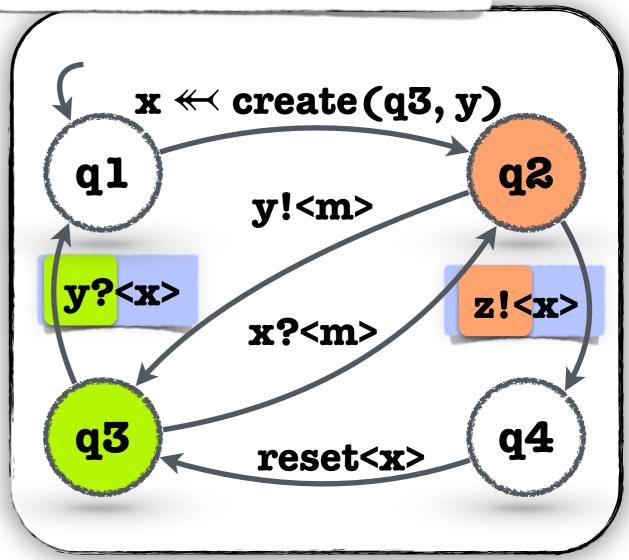

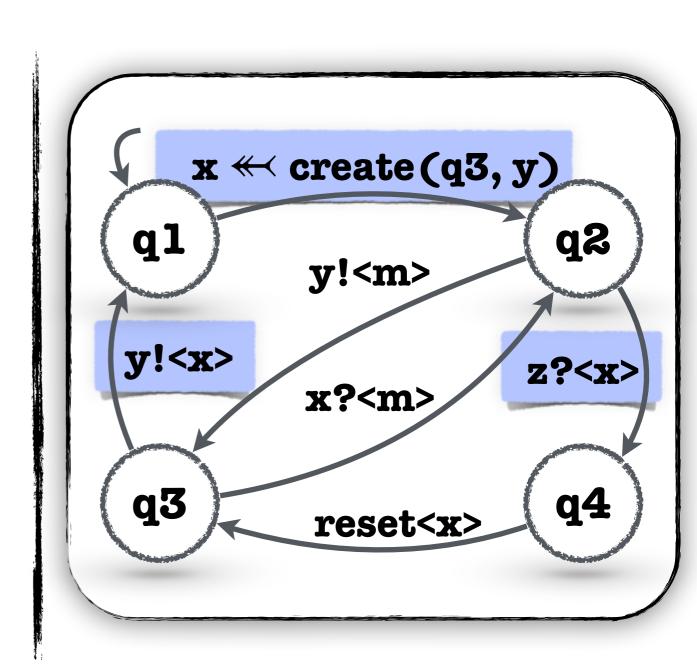

Transitions:

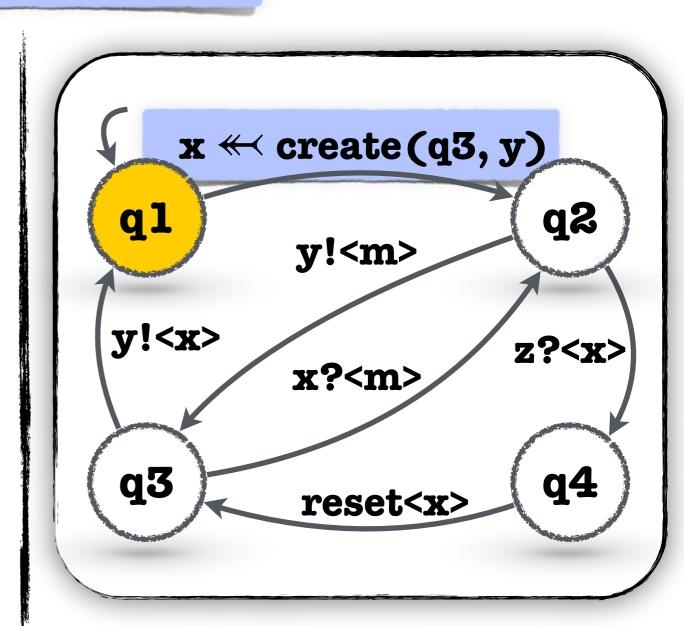

Create Process

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Transitions:

**Create Process**

Send Message

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Transitions:

Create Process

Send Message

Receive Message

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Transitions:

Create Process

Send ID

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Transitions:

Create Process

Send ID

Receive ID

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Transitions:

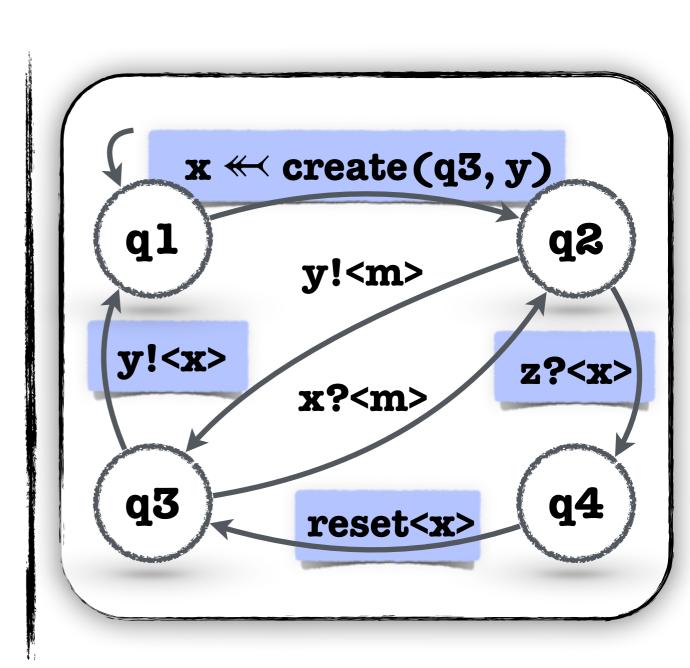

Create Process

Send Msg / ID

Receive Msg / ID

Register Reset

Verification of Dynamic Register Automata

### Formal Model

#### **Process Model**

Finite number of States

Finite number of Registers

Finite message alphabet

Transitions:

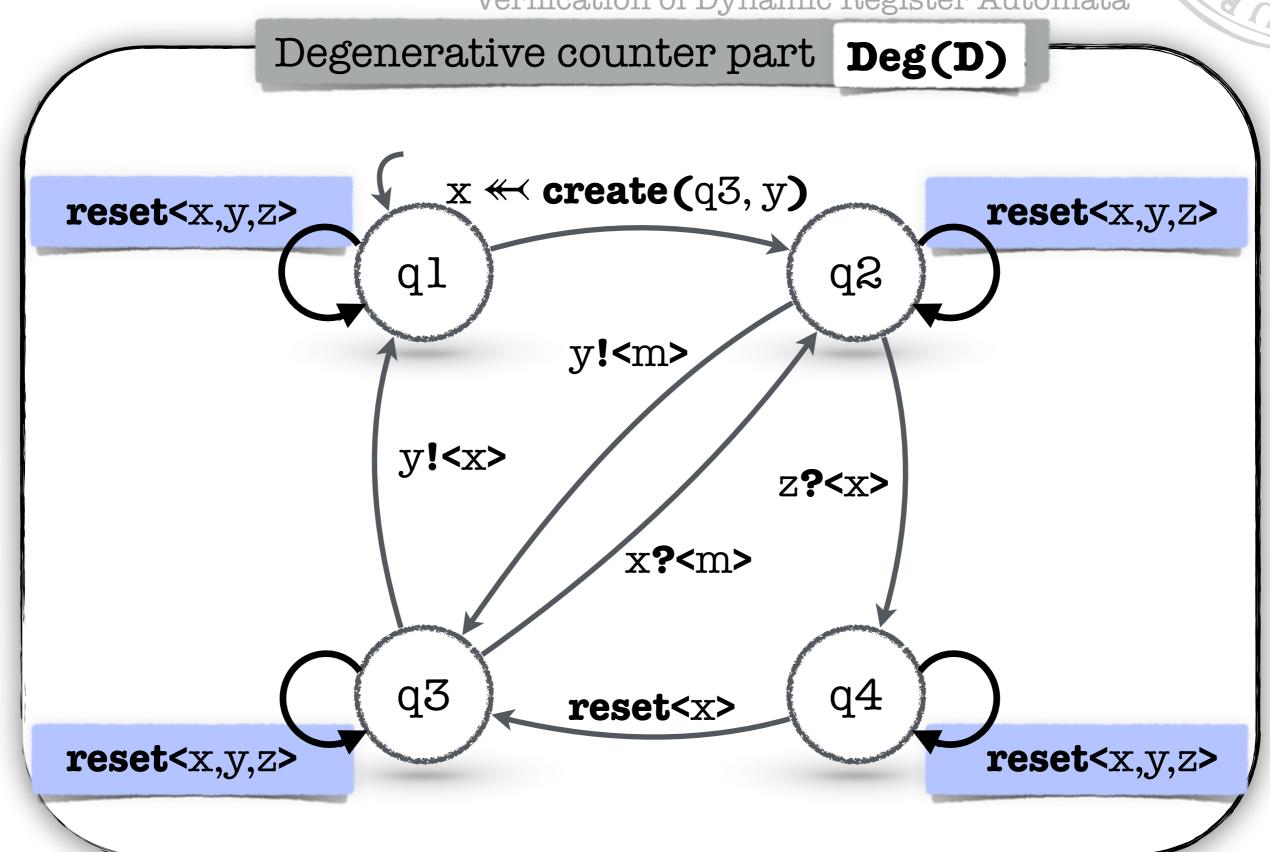

**Create Process**

Send Msg / ID

Receive Msg / ID

Register Reset

Verification of Dynamic Register Automata

### Formal Model

Verification of Dynamic Register Automata

### Formal Model

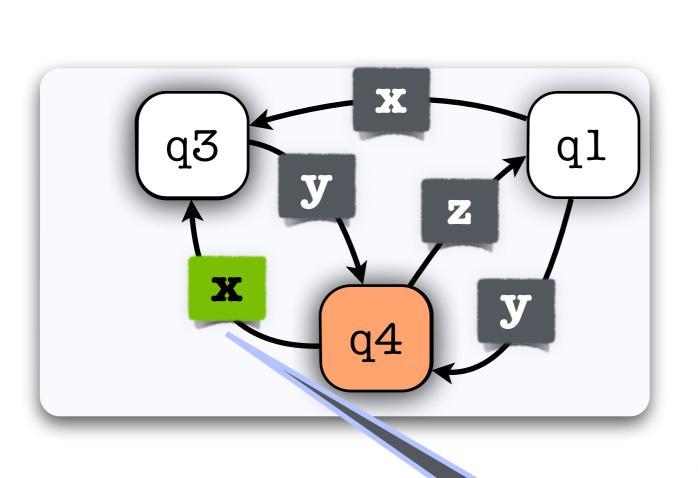

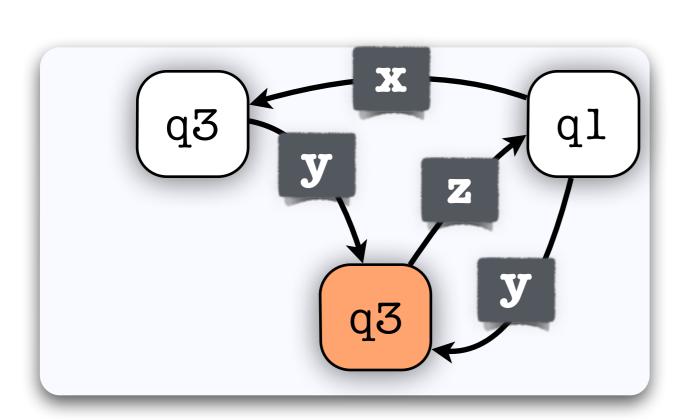

Finite State System

Verification of Dynamic Register Automata

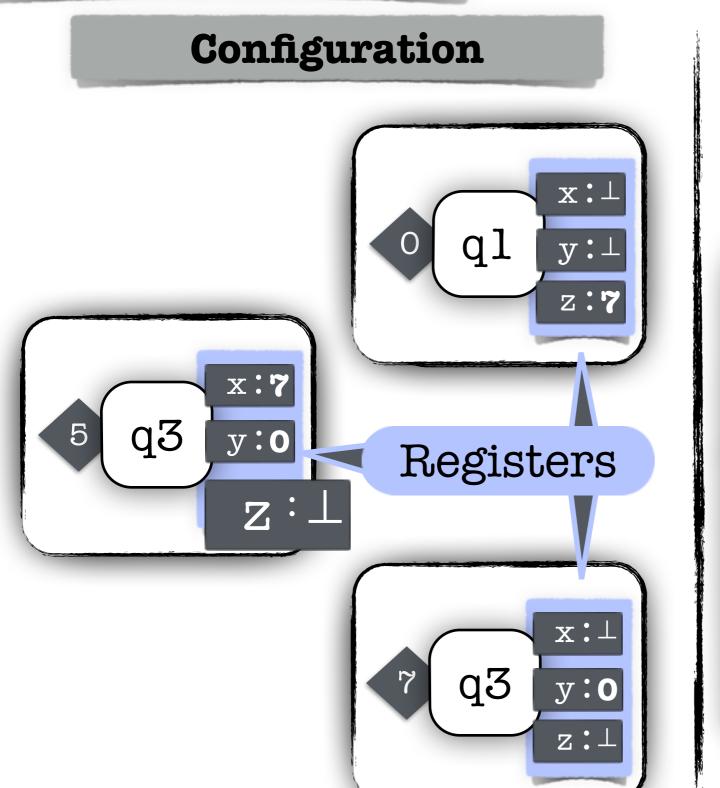

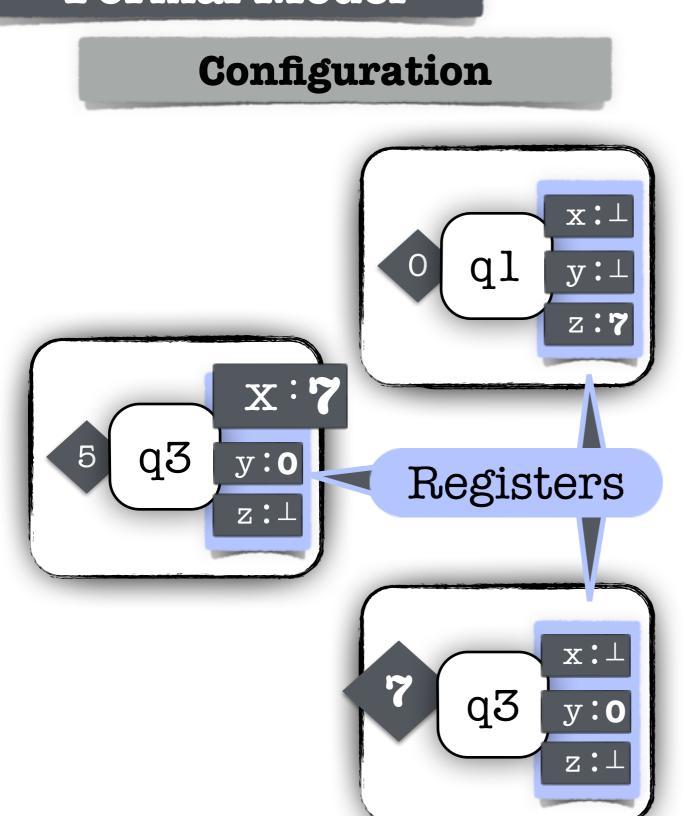

### Formal Model

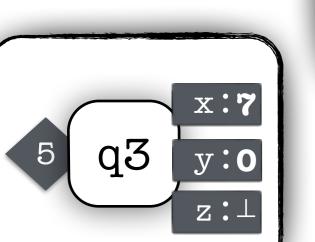

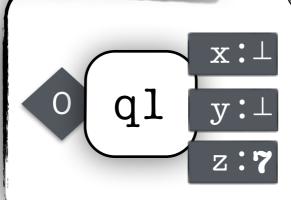

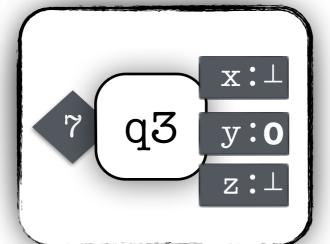

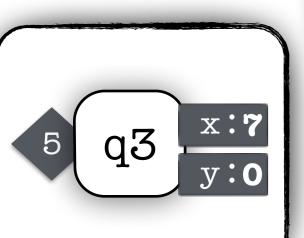

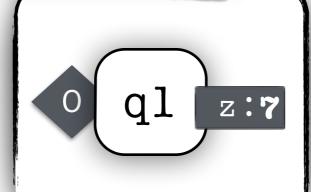

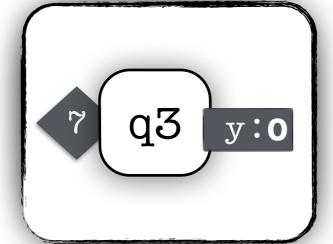

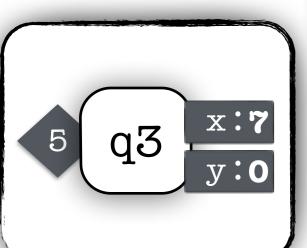

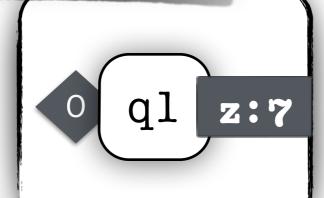

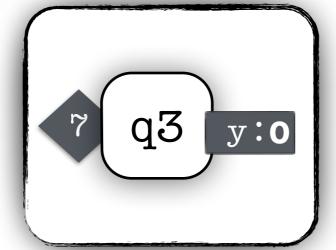

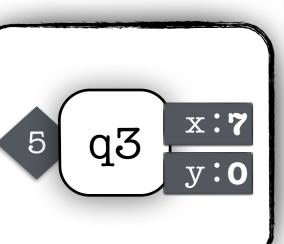

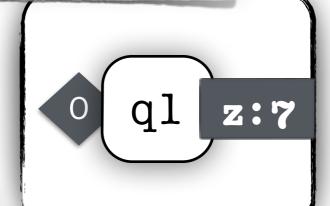

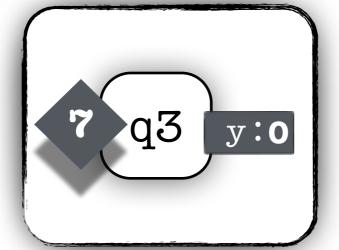

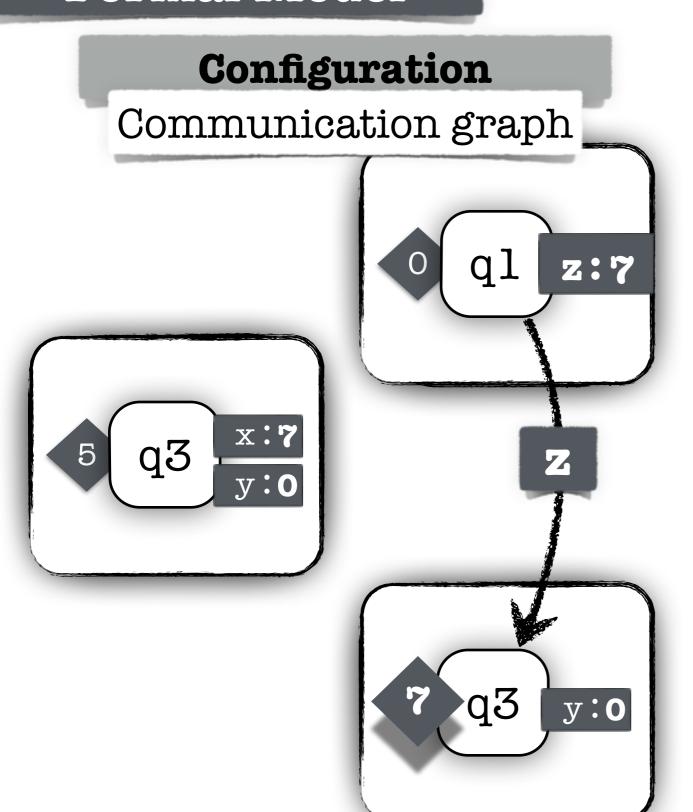

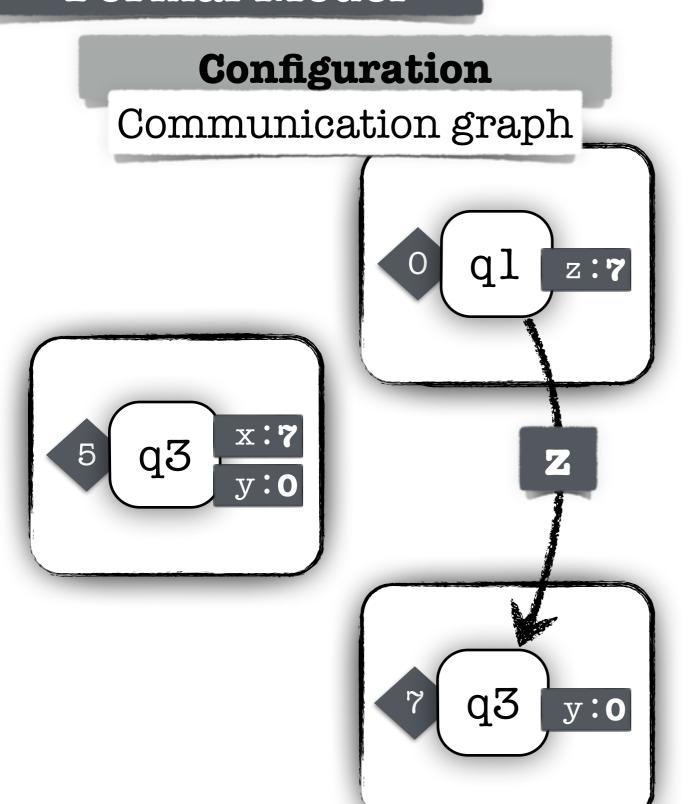

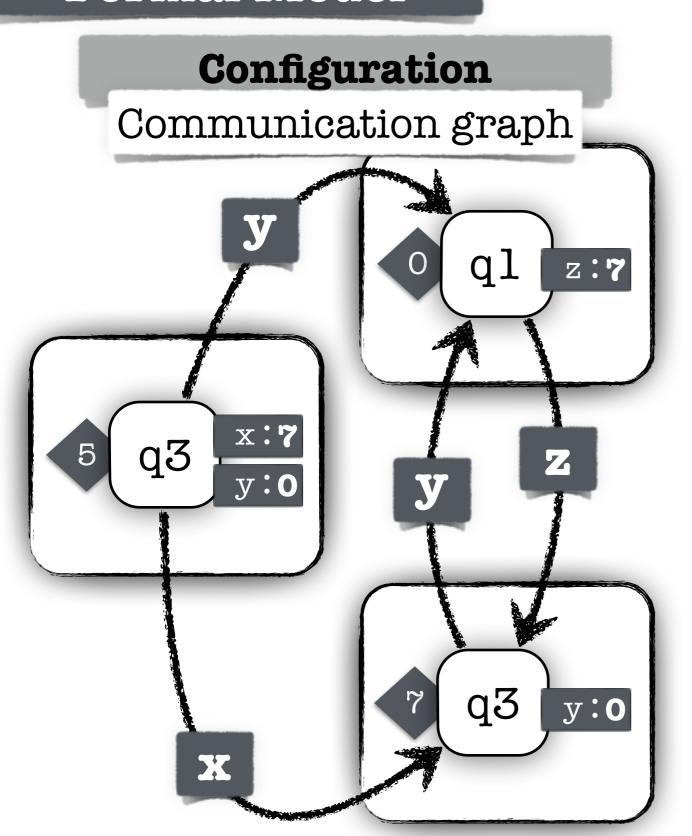

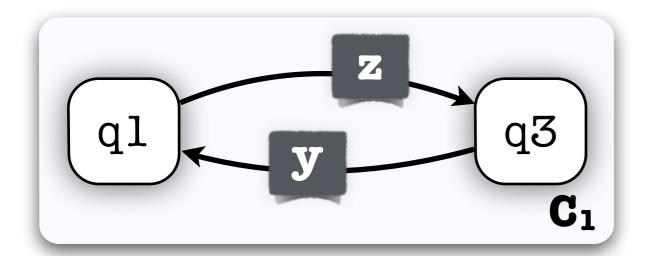

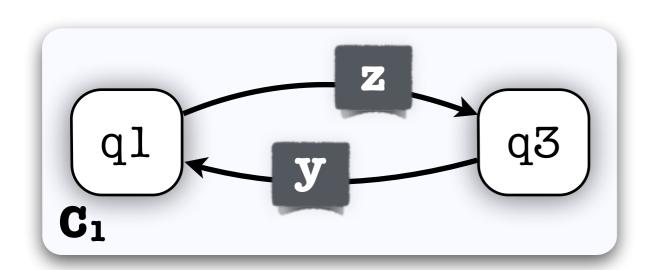

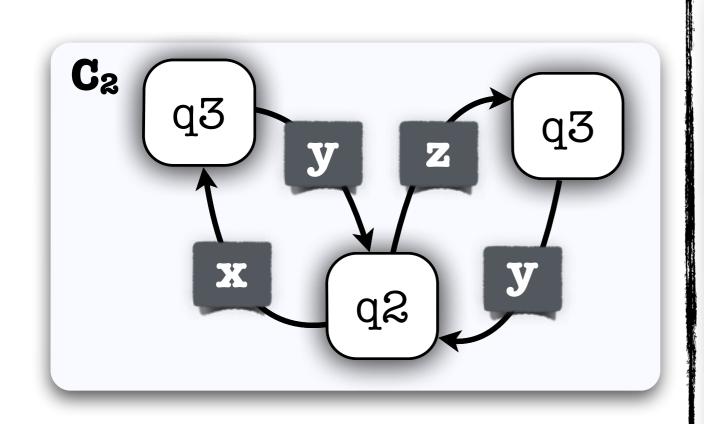

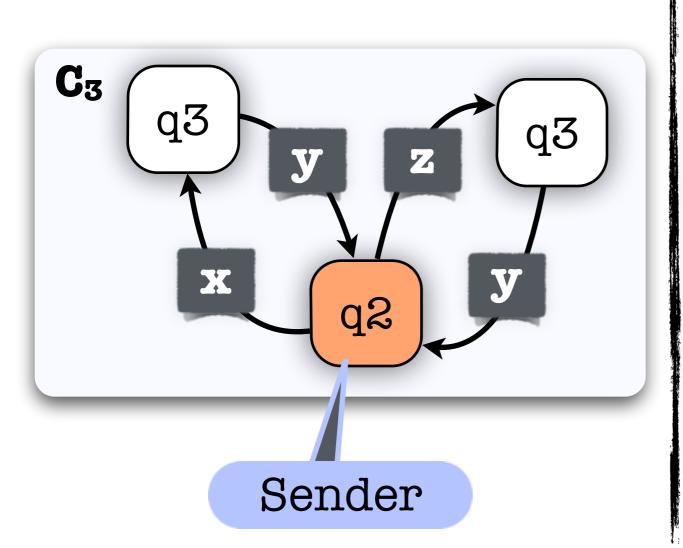

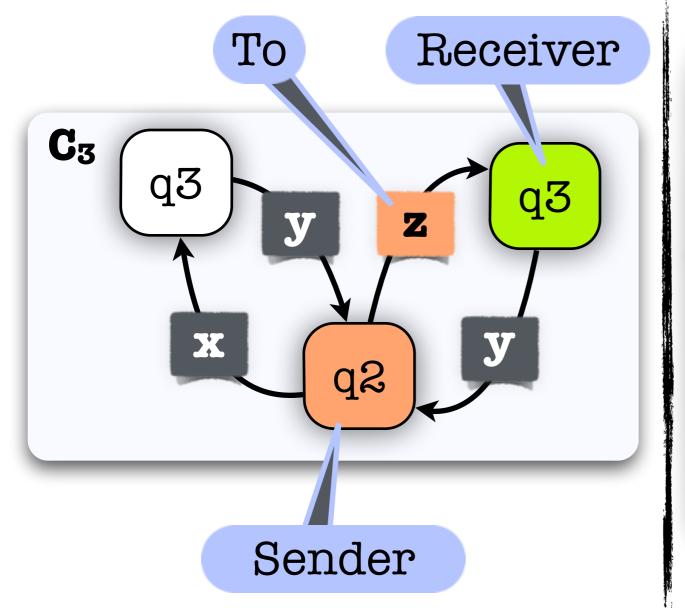

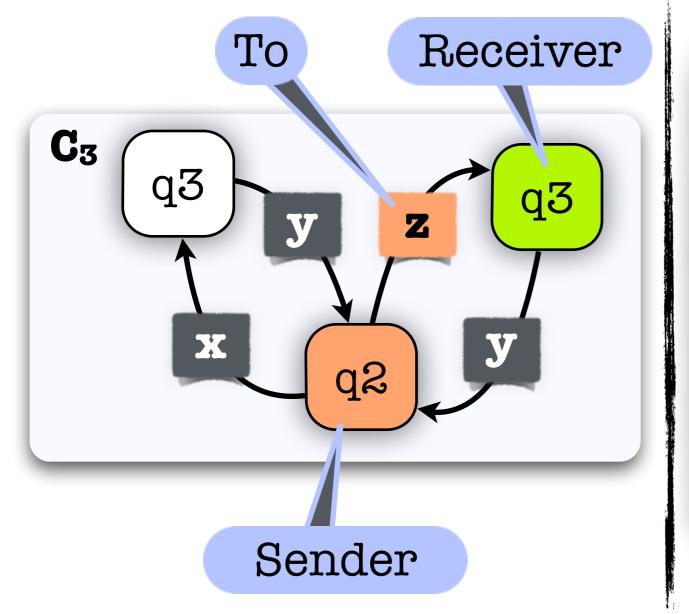

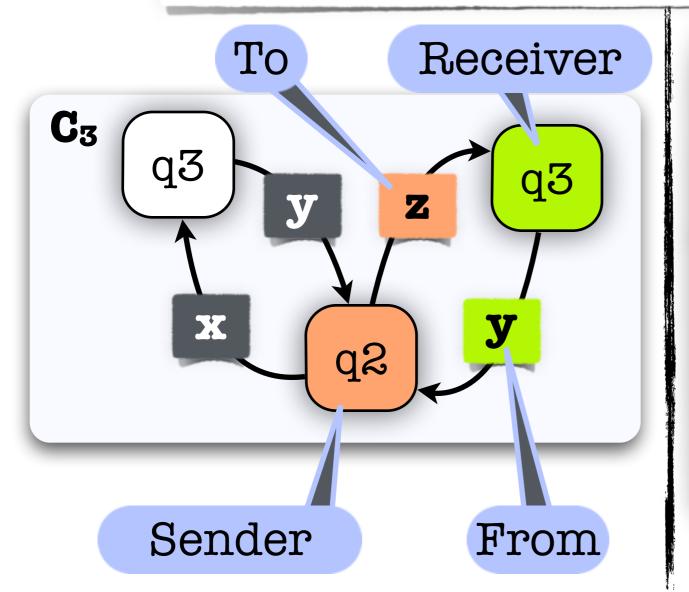

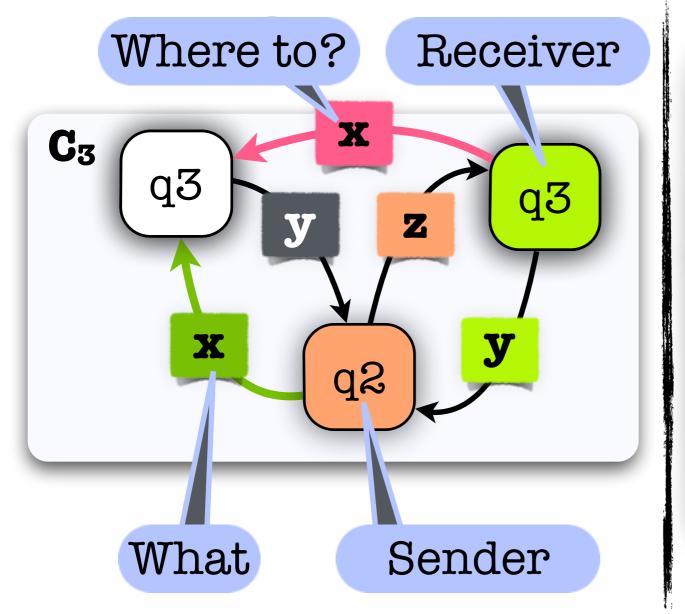

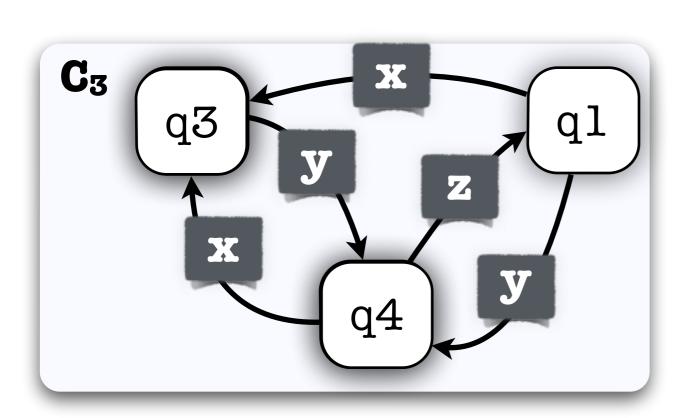

### Configuration

Network of Processes

#### **Process Model**

Finite State System

20

### Formal Model

Verification of Dynamic Register Automata

### Configuration

Network of Processes

#### **Process Model**

Finite State System

Formal Model

Verification of Dynamic Register Automata

22

Formal Model

Verification of Dynamic Register Automata

23

Formal Model

Verification of Dynamic Register Automata

Formal Model

Verification of Dynamic Register Automata

Formal Model

Verification of Dynamic Register Automata

#### Formal Model

Verification of Dynamic Register Automata

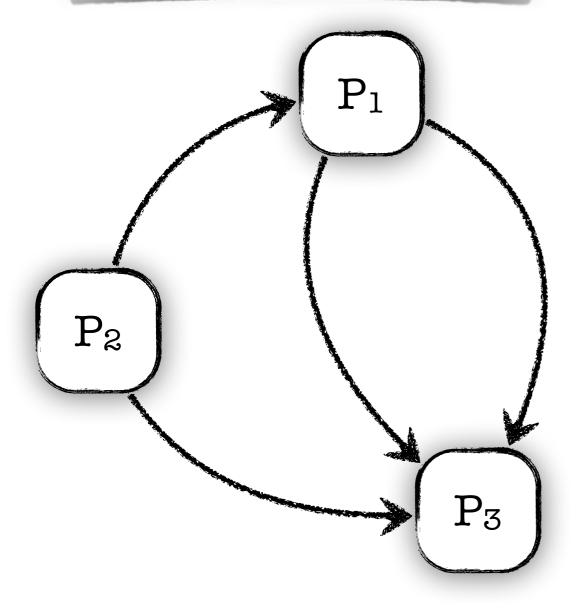

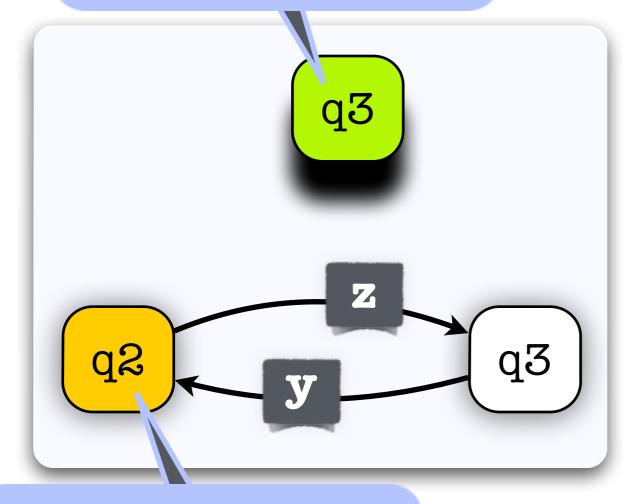

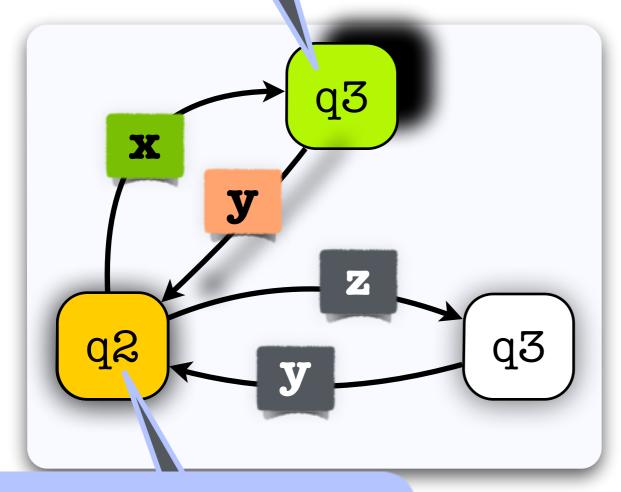

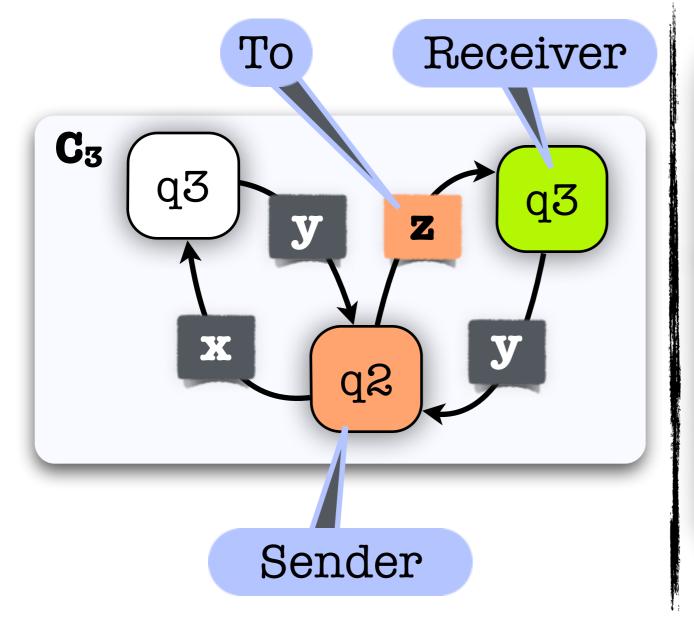

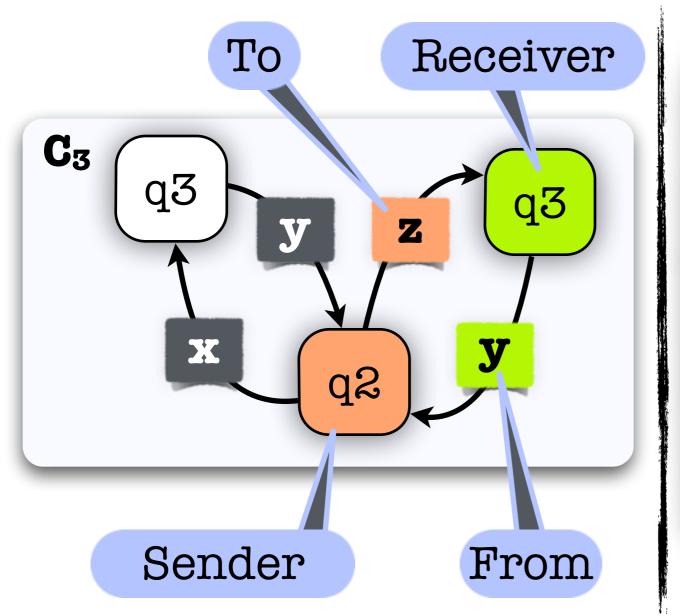

## Configuration

Communication graph

### Formal Model

Verification of Dynamic Register Automata

Communication graph

12/05

### Formal Model

Verification of Dynamic Register Automata

Communication graph

29

### Formal Model

Verification of Dynamic Register Automata

Communication graph

30

### Formal Model

Verification of Dynamic Register Automata

### Formal Model

Verification of Dynamic Register Automata

### Formal Model

Verification of Dynamic Register Automata

Formal Model

Verification of Dynamic Register Automata

### Configuration

Communication graph

### Formal Model

Verification of Dynamic Register Automata

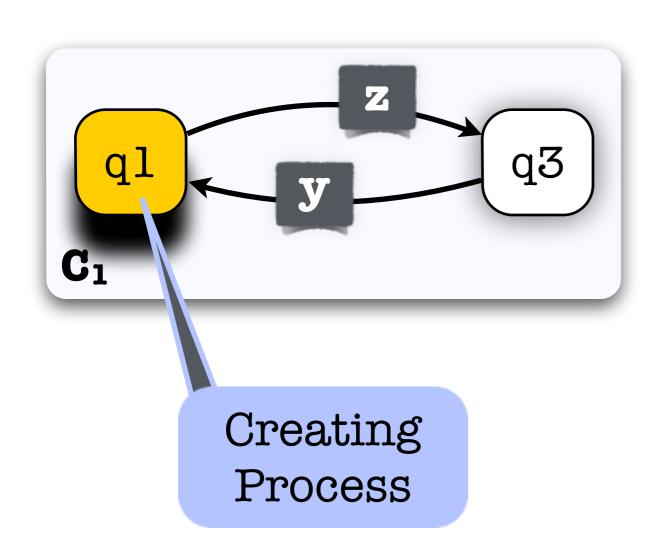

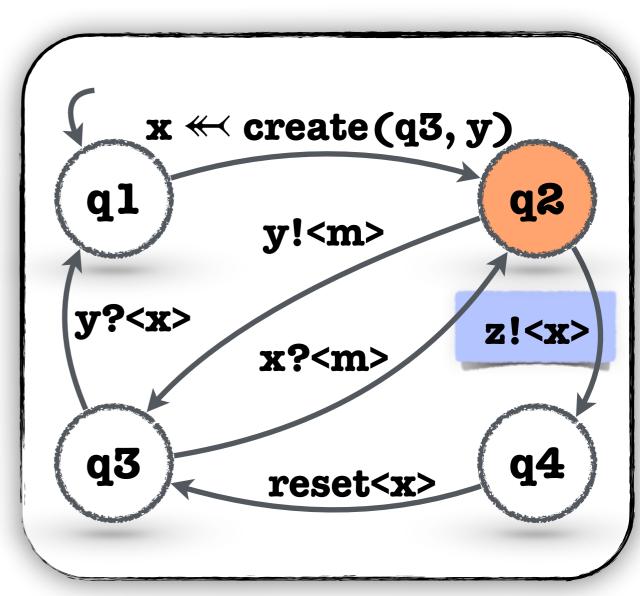

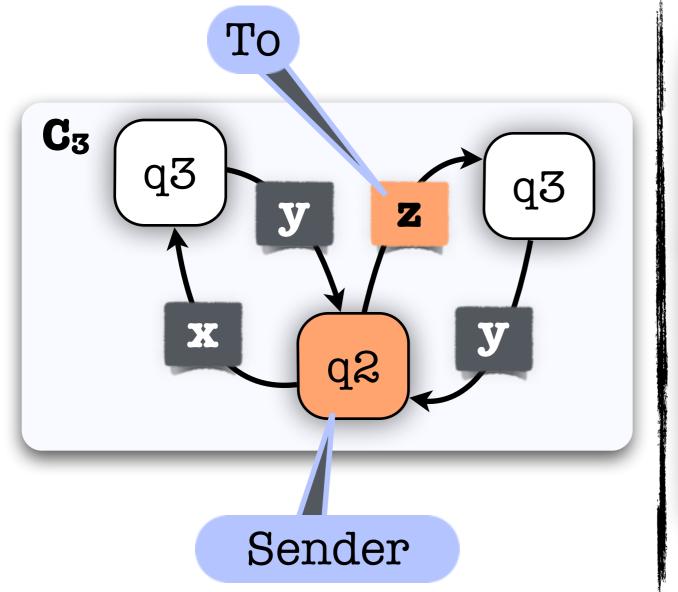

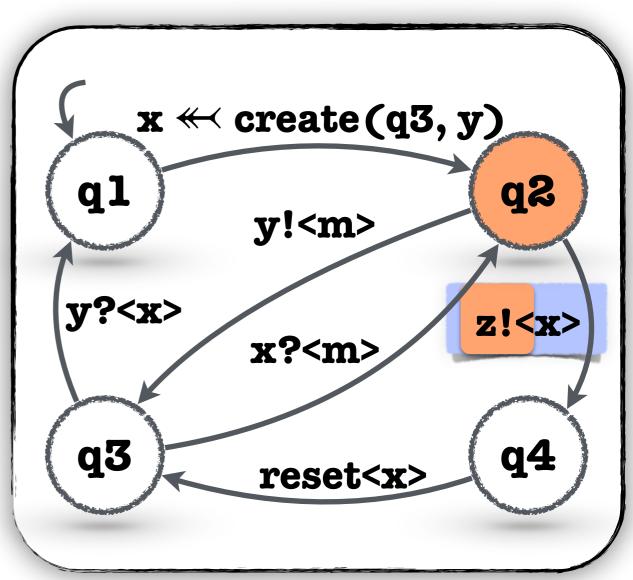

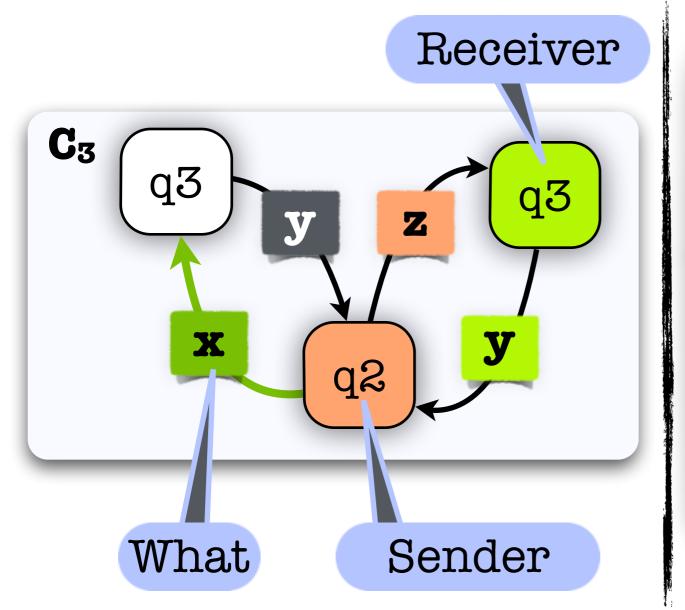

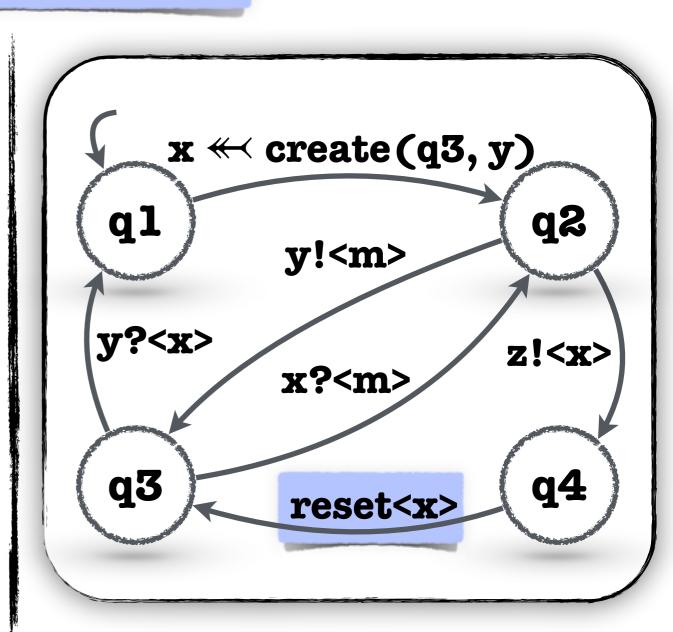

Configuration

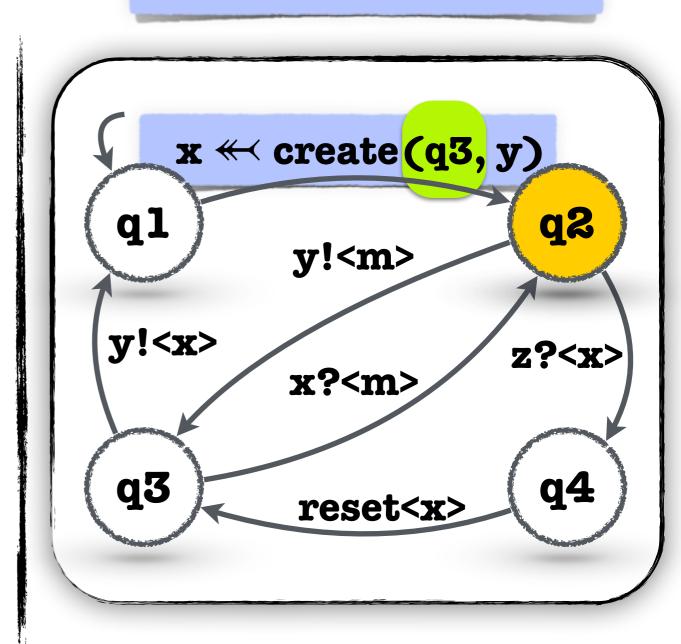

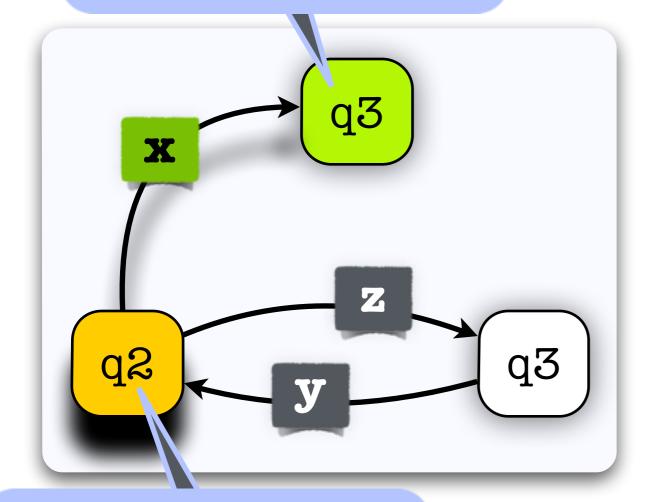

**Transition Relation**

3

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

**Process Creation**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

**Process Creation**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

38

Formal Model

Verification of Dynamic Register Automata

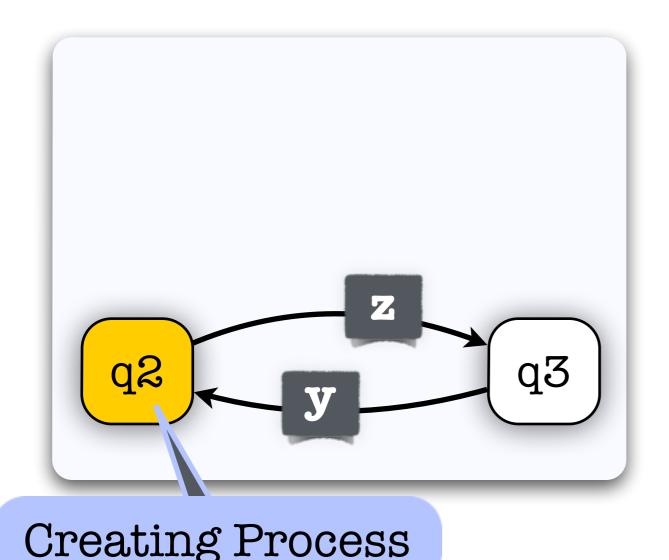

Configuration

Transition Relation

**Created Process**

**Creating Process**

**Process Model**

38

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Created Process**

Creating Process

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Created Process**

**Creating Process**

**Process Model**

Formal Model

Verification of Dynamic Register Automata

# Configuration Transition Relation

#### **Process Model**

42

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

50

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

**Formal Model**

Verification of Dynamic Register Automata

Configuration

**Transition Relation**

**Process Model**

Send & Receive ID

Point-To-Point, Rendez-Vous communication

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

55

Formal Model

Verification of Dynamic Register Automata

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

58

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Send & Receive ID

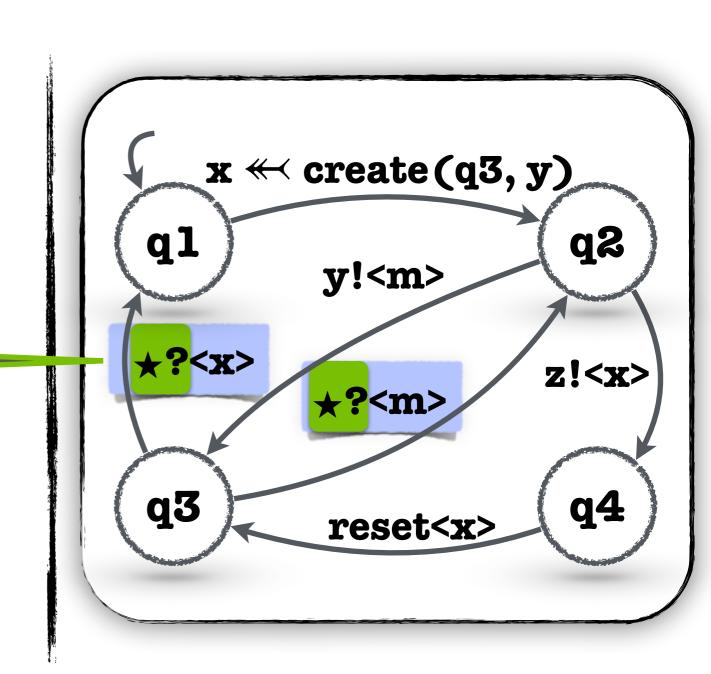

Selective Receive

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Send & Receive ID

Non Selective Receive

UUIIIAUA

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Send & Receive ID

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

Register Reset

Which register

Formal Model

Verification of Dynamic Register Automata

Configuration

Transition Relation

**Process Model**

#### Formal Model

Verification of Dynamic Register Automata

## Configuration Transition Relation

#### **Process Model**

Formal Model

Verification of Dynamic Register Automata

Configuration

**Process Model**

**Transition Relation**

**Process Creation**

Send & Receive ID

Verification of Dynamic Register Automata

**Applications**

Formal Model

**Process Model**

Configuration

**Transition Relation**

Verification of Dynamic Register Automata

**Applications**

Formal Model

State Reachability

State Reachability

Verification of Dynamic Register Automata

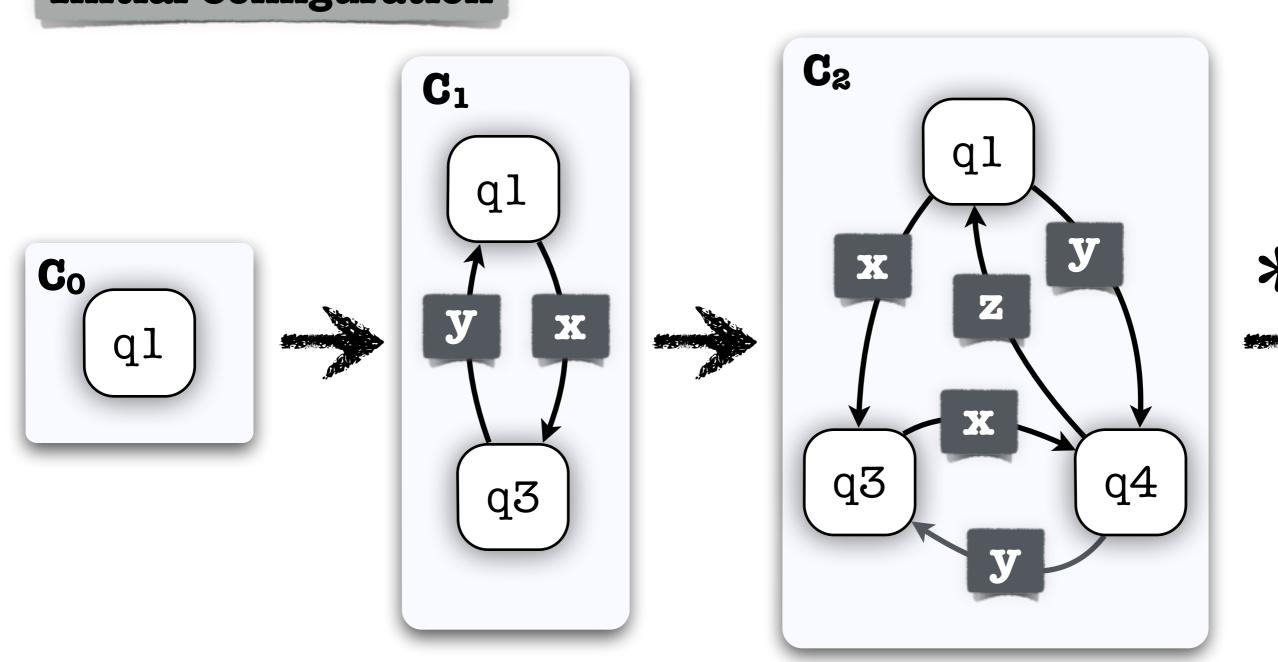

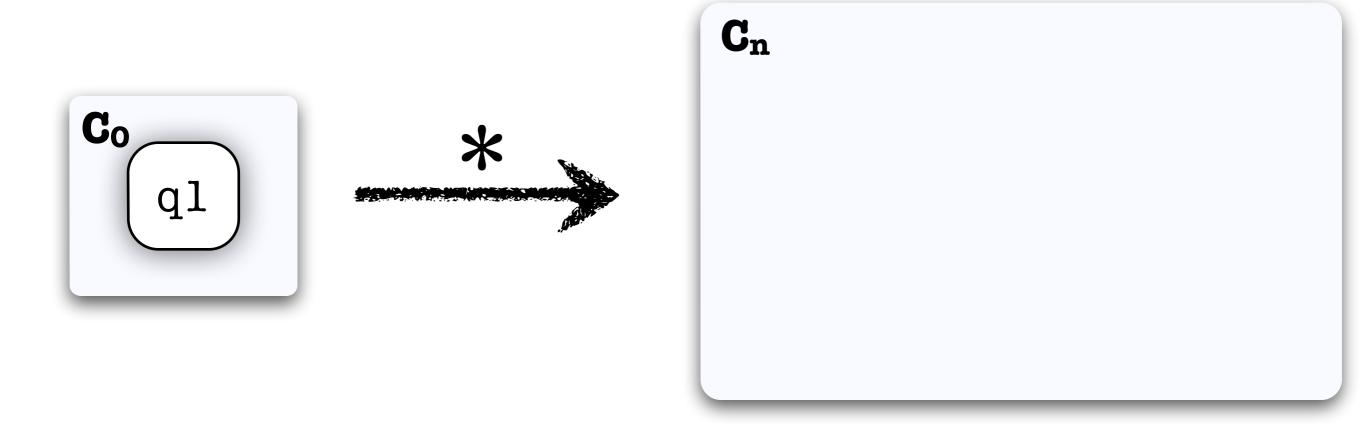

**Initial Configuration**

State Reachability

Initial Configuration

Verification of Dynamic Register Automata

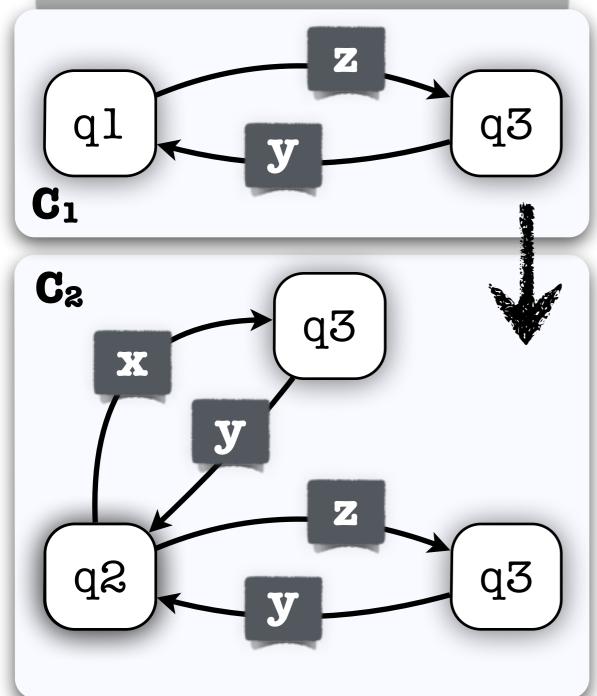

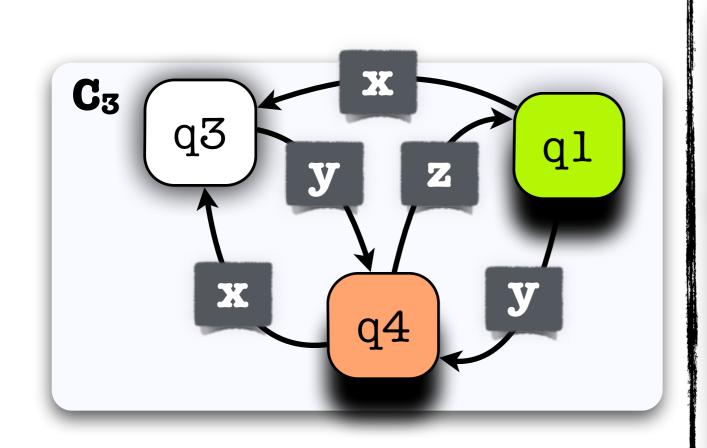

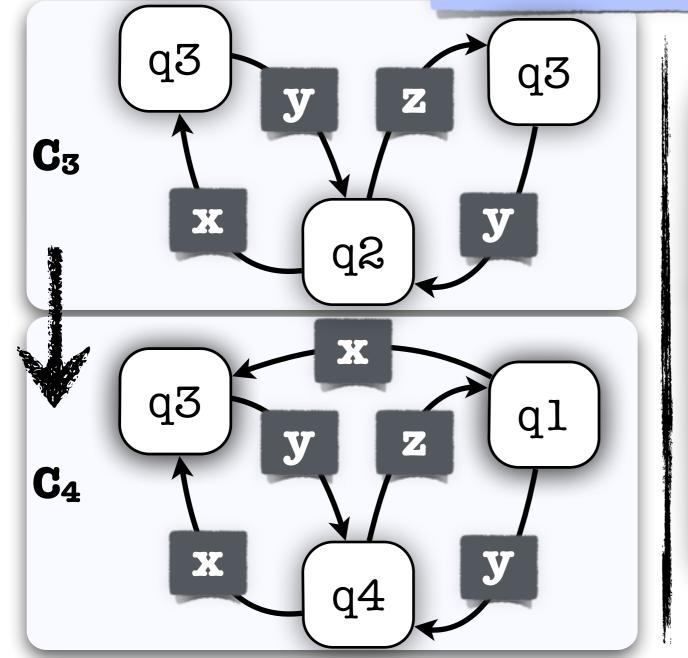

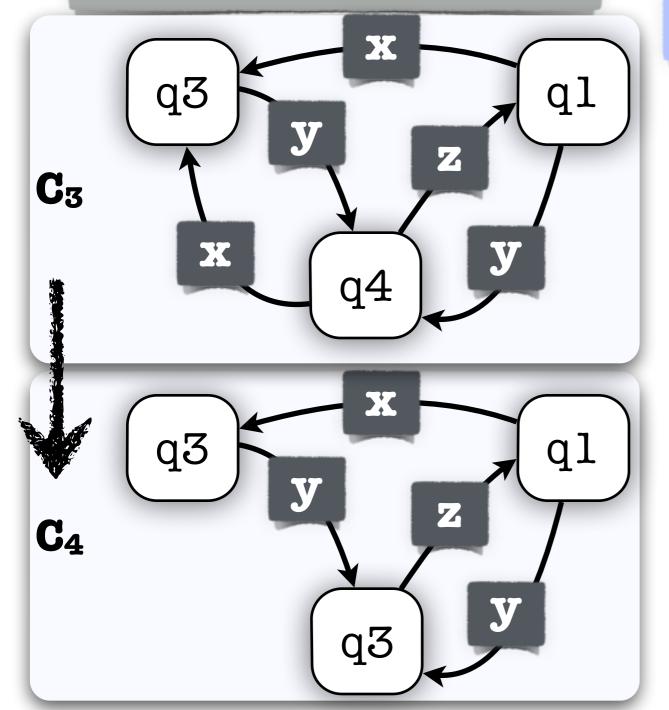

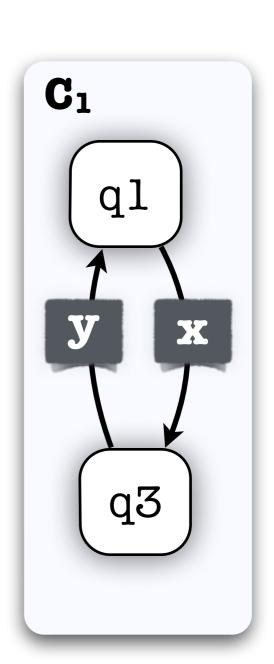

Run: Co

State Reachability

Initial Configuration

Verification of Dynamic Register Automata

Run:  $C_0$ ,  $C_1$

State Reachability

Initial Configuration

Verification of Dynamic Register Automata

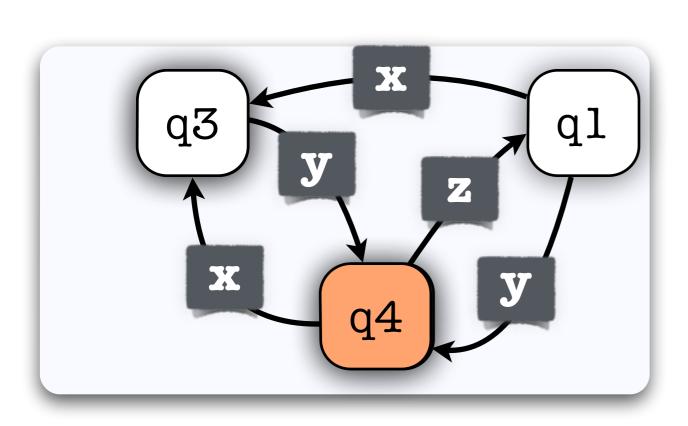

Ca  $C_1$ ql ql X Co X ql q3 **q4** q3

Run: C<sub>0</sub>, C<sub>1</sub>, C<sub>2</sub>

74

State Reachability

Initial Configuration

Verification of Dynamic Register Automata

Run:  $C_0$ ,  $C_1$ ,  $C_2$ , ...

State Reachability

Initial Configuration

Verification of Dynamic Register Automata

Run:  $C_0, C_1, C_2, ..., C_n$

State Reachability

**Initial Configuration**

Run:  $C_0, C_1, C_2, ..., C_n$

Verification of Dynamic Register Automata

State Reachability Problem:

State Reachability

Initial Configuration

Run: Co, C1, C2, ..., Cn

Verification of Dynamic Register Automata

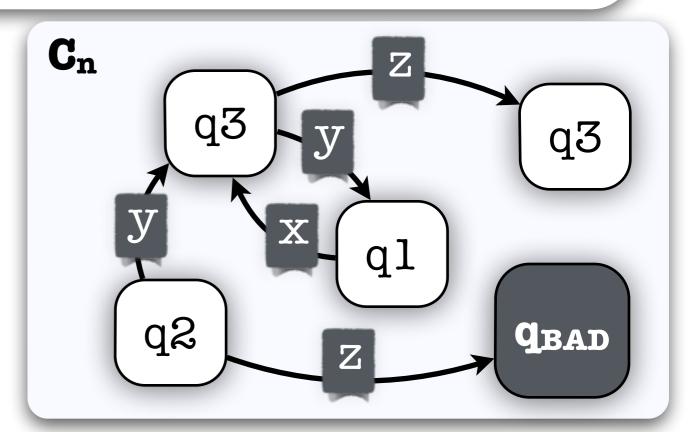

#### State Reachability Problem:

Given a control state  $\mathbf{q_{BAD}}$ , is there a run starting from the initial configuration that reaches a configuration where  $\mathbf{q_{BAD}}$  occurs.

State Reachability

**Initial Configuration**

Run:  $C_0$ ,  $C_1$ ,  $C_2$ , ...,  $C_n$

Verification of Dynamic Register Automata

#### State Reachability Problem:

Given a control state  $q_{BAD}$ , is there a run starting from the initial configuration that reaches a configuration where **q<sub>BAD</sub>** occurs.

State Reachability

Verification of Dynamic Register Automata

**Initial Configuration**

Run:  $C_0$ ,  $C_1$ ,  $C_2$ , ...,  $C_n$

#### State Reachability Problem:

Given a control state  $\mathbf{q_{BAD}}$ , is there a run starting from the initial configuration that reaches a configuration where  $\mathbf{q_{BAD}}$  occurs.

Verification of Dynamic Register Automata

Applications

Formal Model

State Reachability

Undecidable

#### State Reachability

Study of the decidability and complexity for different sub-classes of the problem

80

### State Reachability

Study of the decidability and complexity for different sub-classes of the problem

**Bounded DRA**

Undecidable

80

Verification of Dynamic Register Automata

#### State Reachability

Study of the decidability and complexity for different sub-classes of the problem

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

#### State Reachability

Study of the decidability and complexity for different sub-classes of the problem

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

Decidable

**Non-Primitive Recursive**

80

Verification of Dynamic Register Automata

#### State Reachability

Study of the decidability and complexity for different sub-classes of the problem

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

Decidable

**Non-Primitive Recursive**

\\&\

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

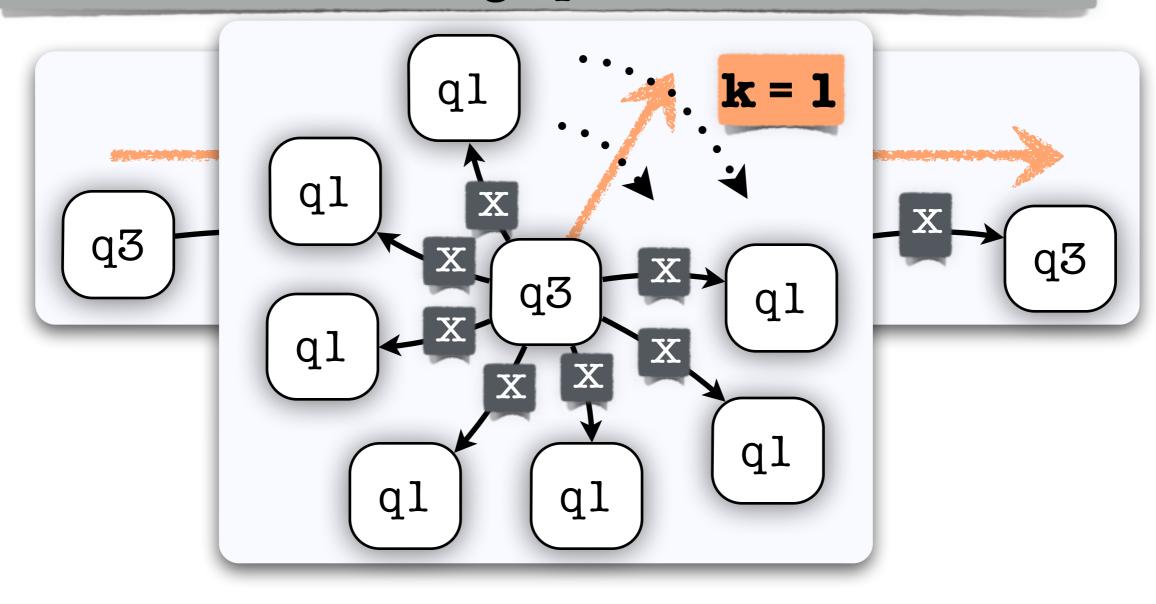

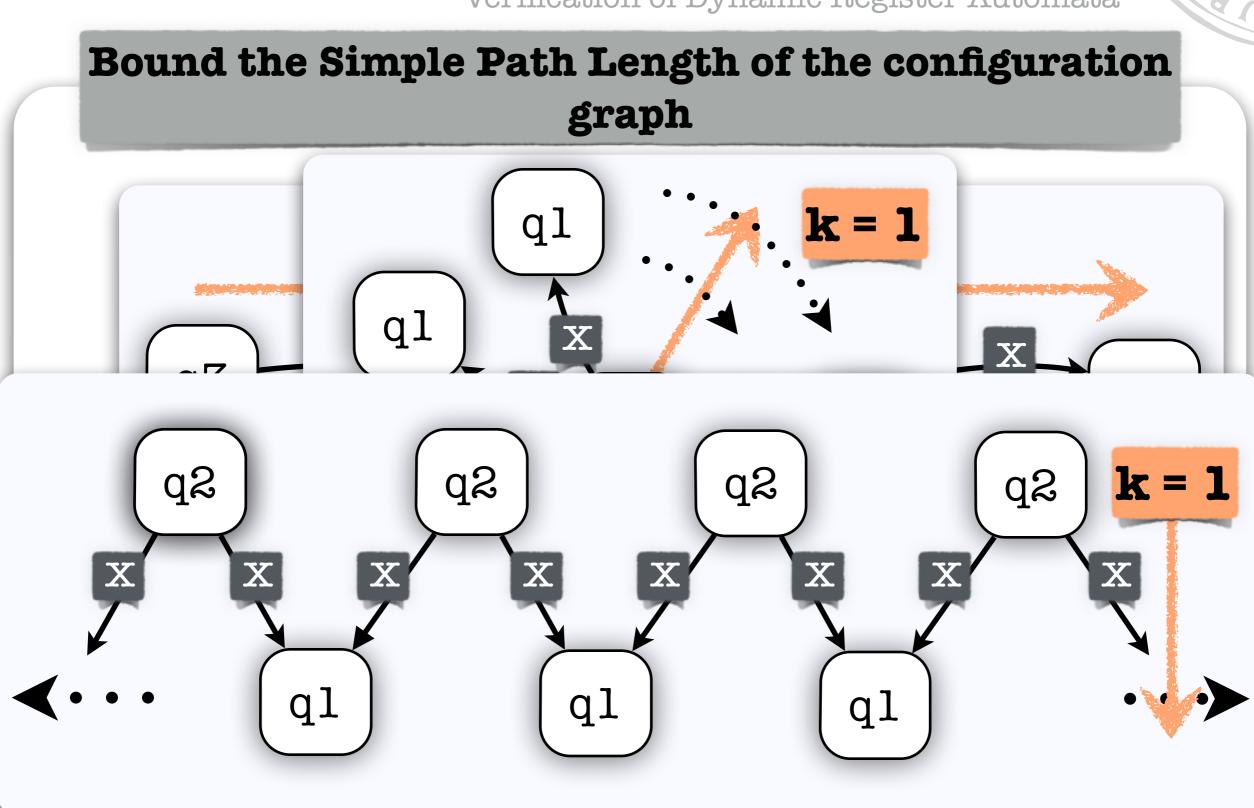

## Bound the Simple Path Length of the configuration graph

**Using Rendez-Vous Communication**

Verification of Dynamic Register Automata

## Bound the Simple Path Length of the configuration graph

**Using Rendez-Vous Communication**

## Bound the Simple Path Length of the configuration graph

**Using Rendez-Vous Communication**

Verification of Dynamic Register Automata

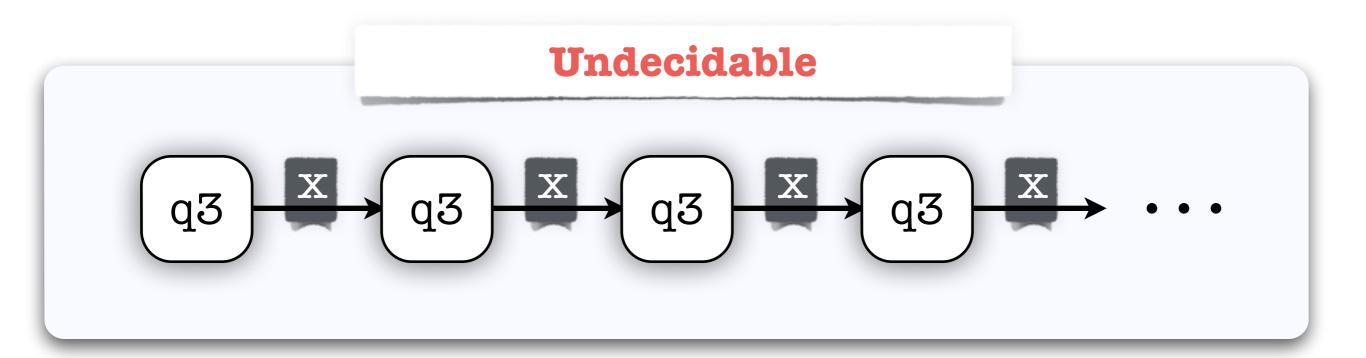

# Bound the Simple Path Length of the configuration graph

Undecidable

#### Contribution

Verification of Dynamic Register Automata

### State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

**Decidable**

**Non-Primitive Recursive**

#### Contribution

Verification of Dynamic Register Automata

### State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

**Decidable**

**Non-Primitive Recursive**

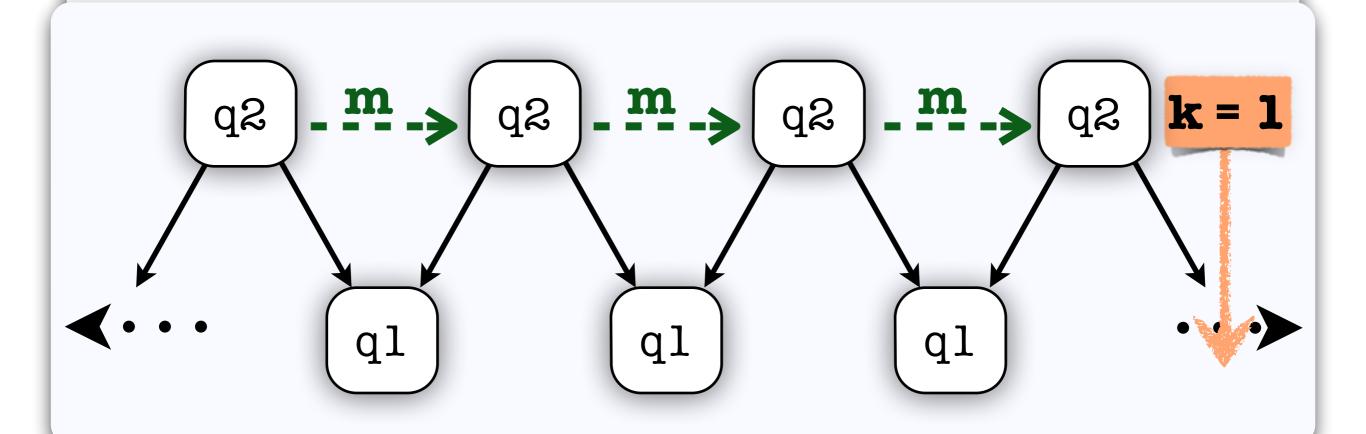

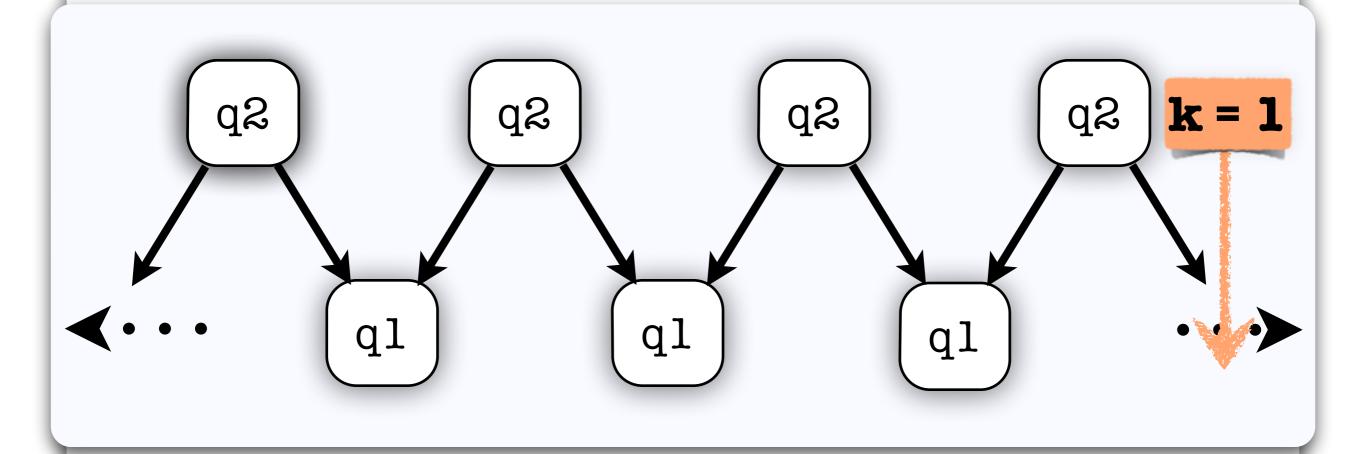

## Strongly Bounded DRA

Verification of Dynamic Register Automata

### Strongly Bounded DRA

Verification of Dynamic Register Automata

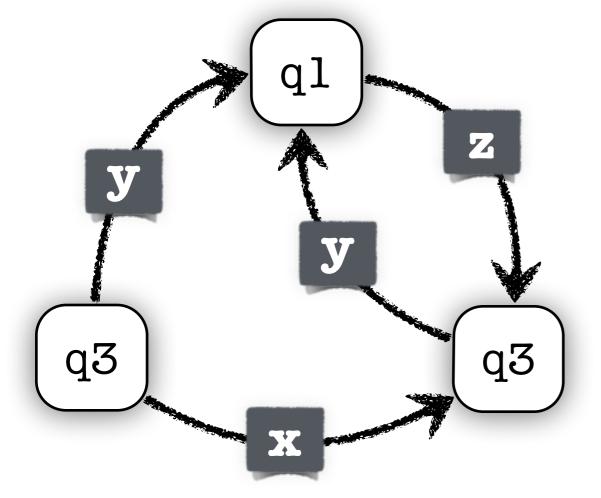

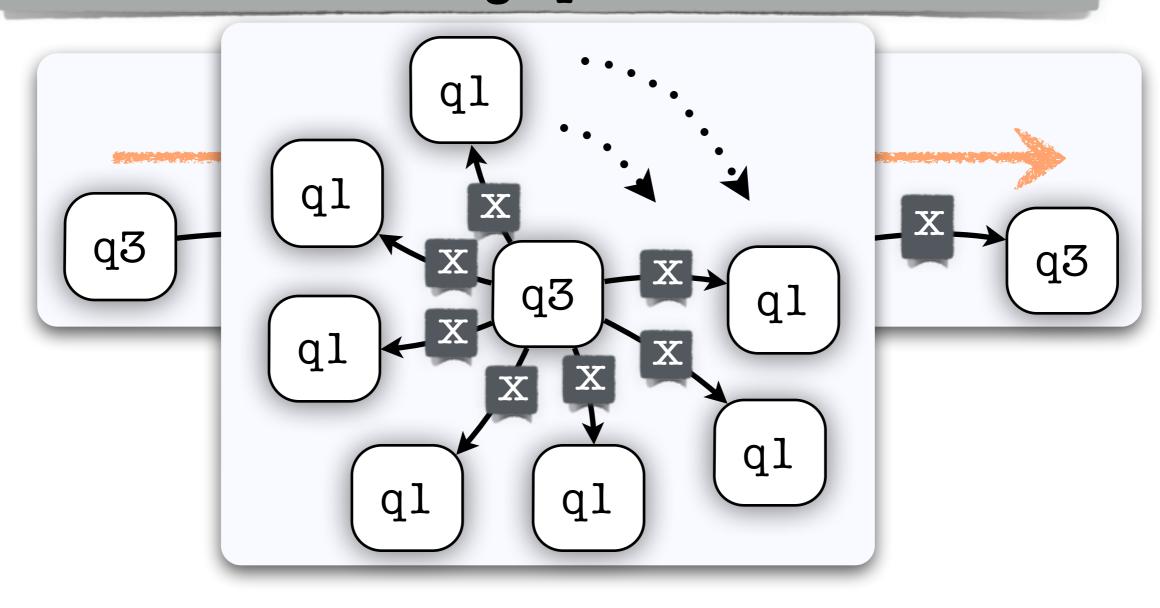

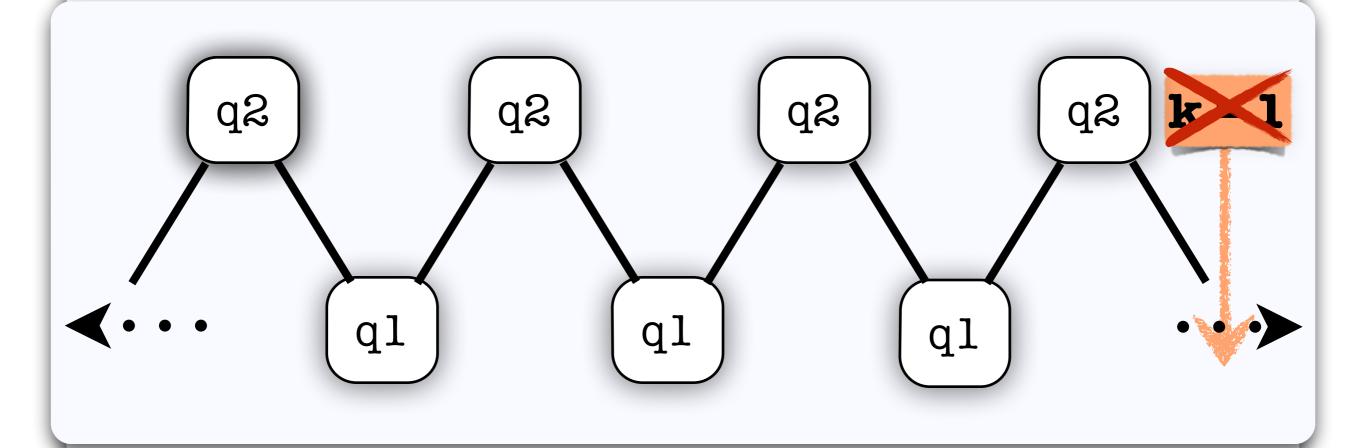

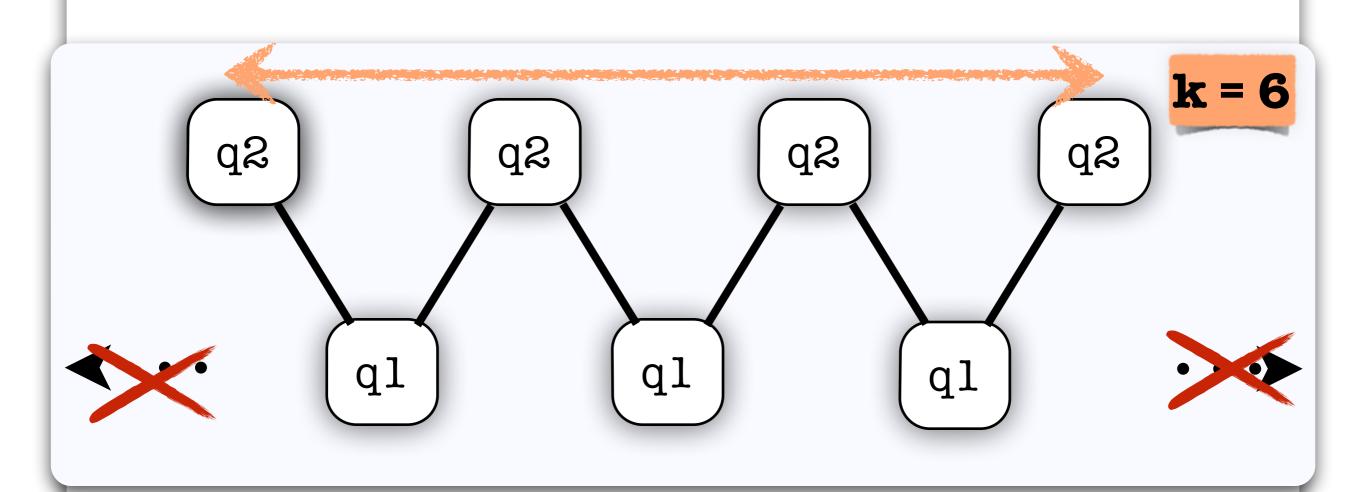

Bound the Simple Path Length of the underlying undirected configuration graph

Still: Unbounded Number of Processes

Bound the Simple Path Length of the underlying undirected configuration graph

Undecidable

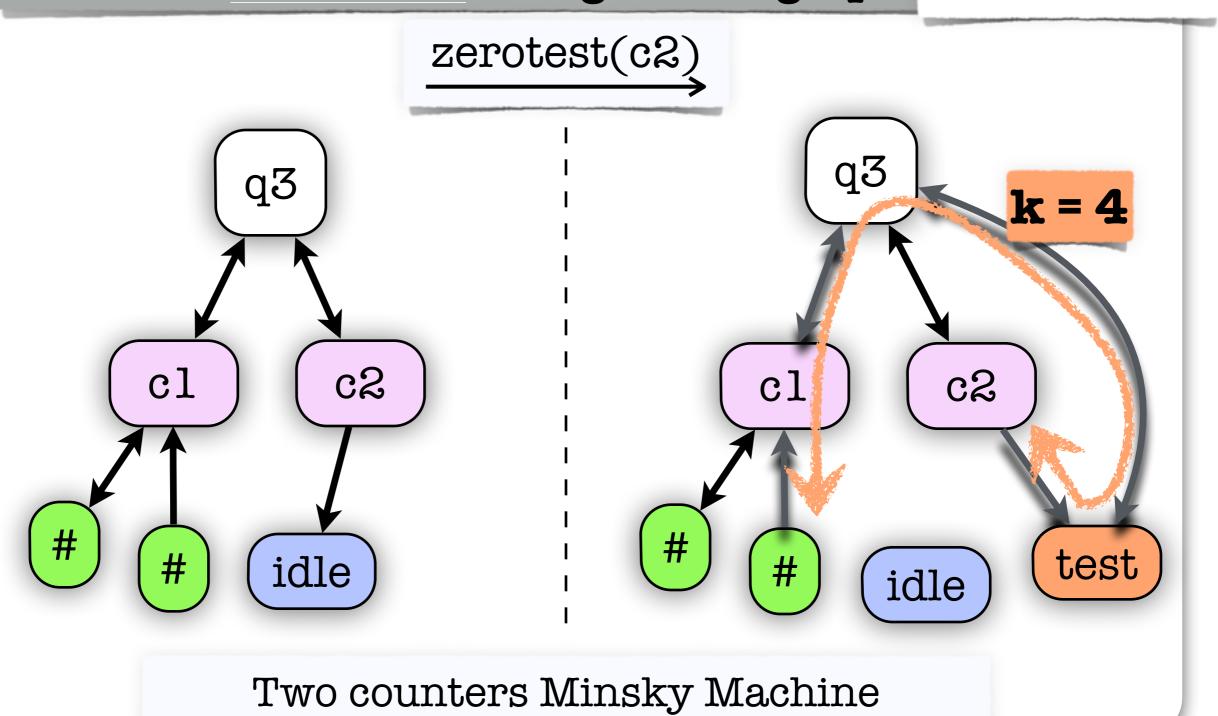

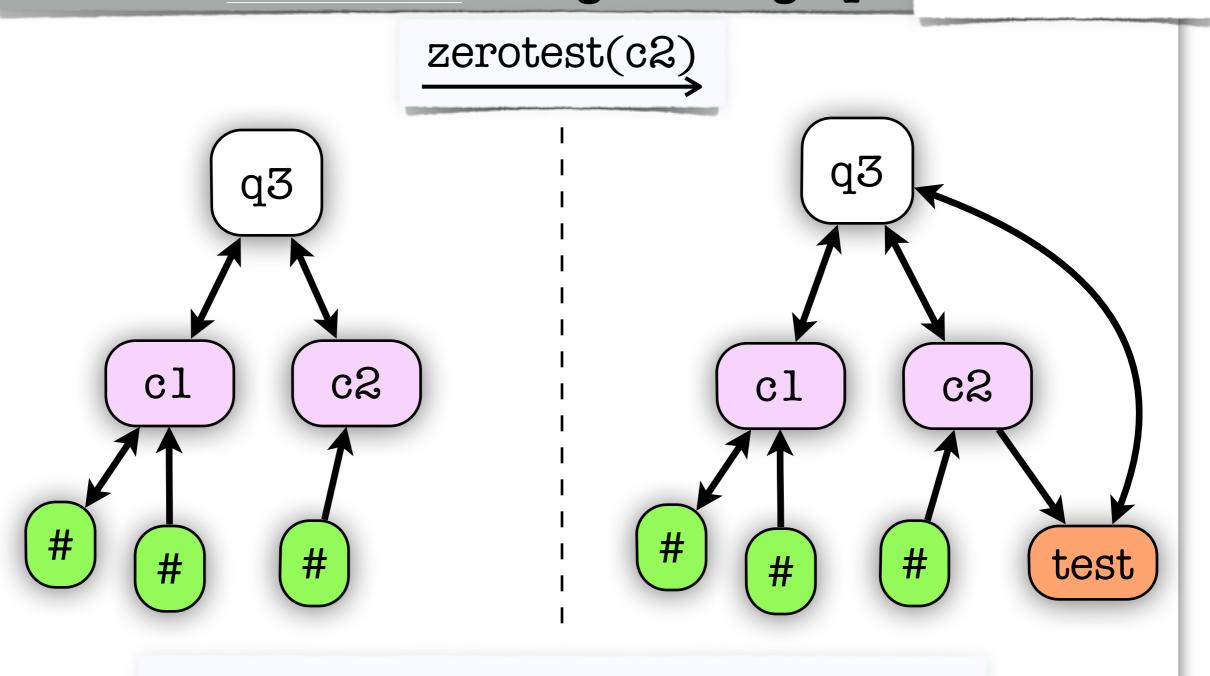

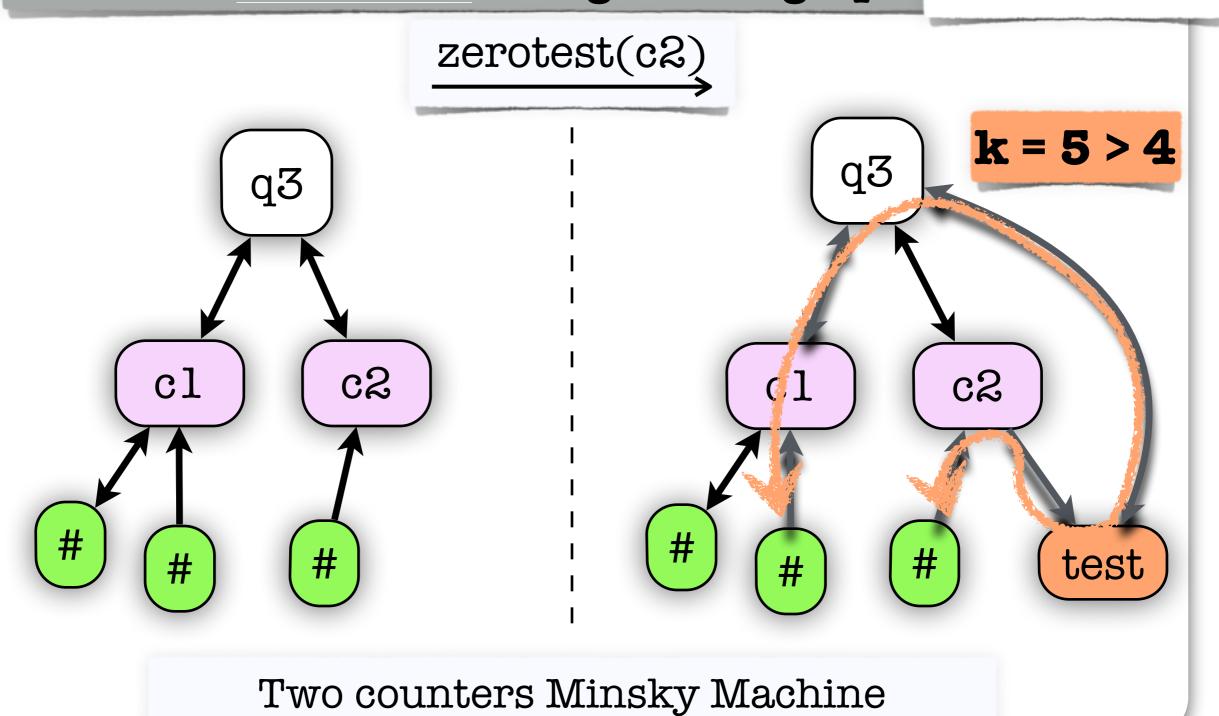

# Bound the Simple Path Length of the underlying undirected configuration graph Undecidable

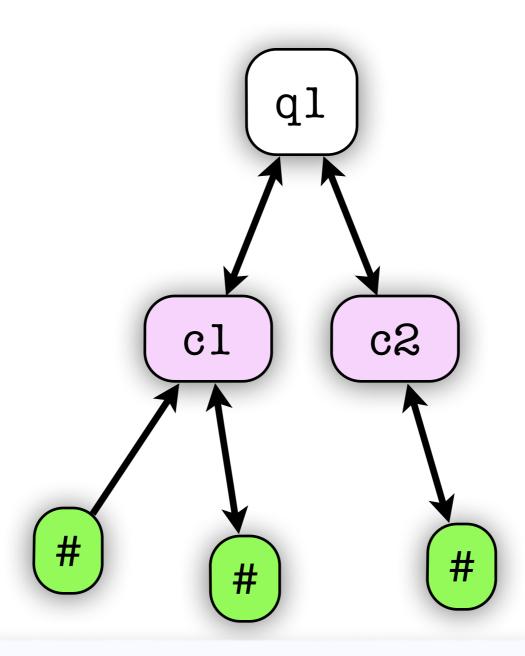

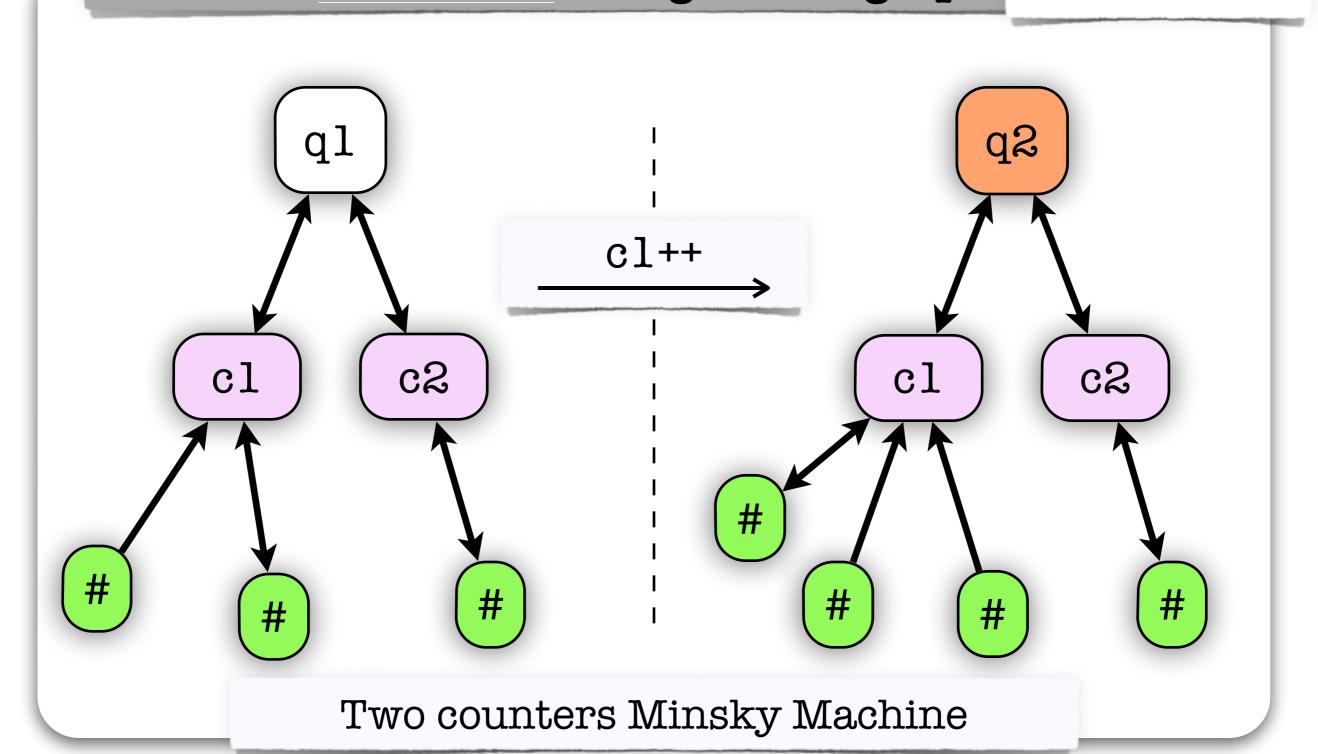

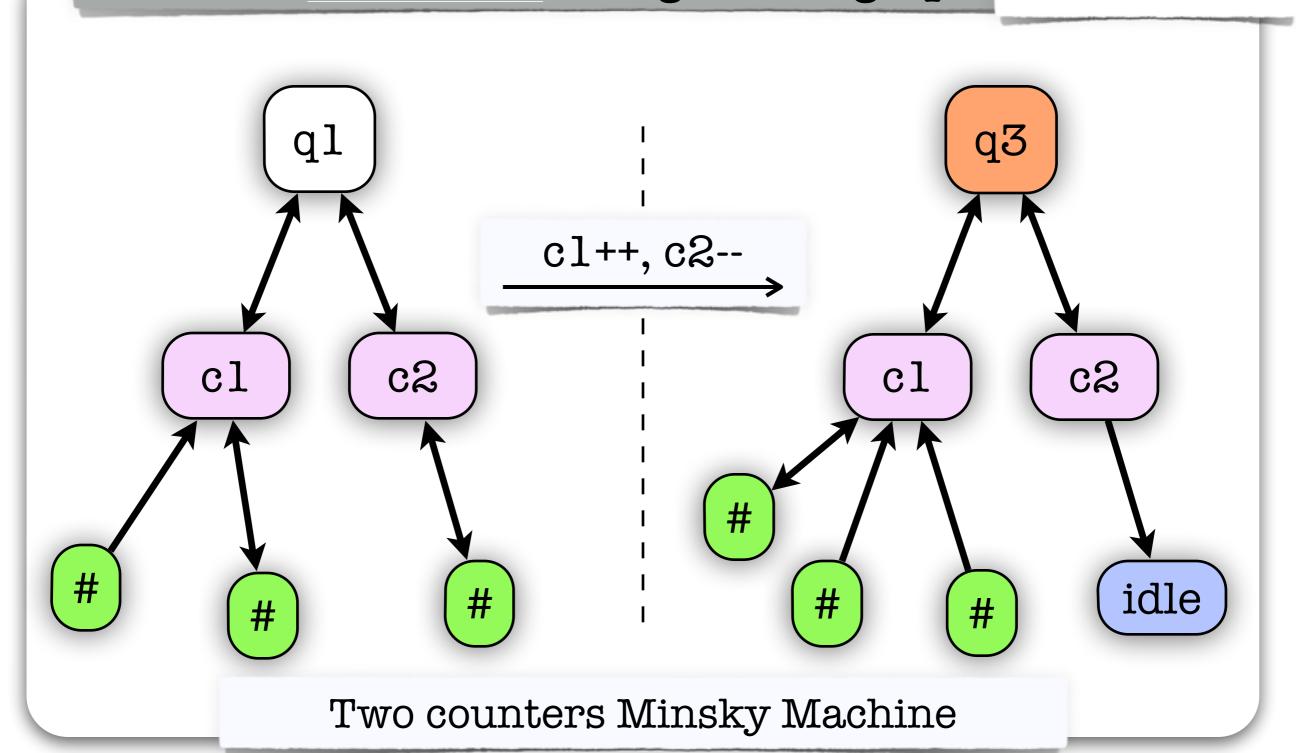

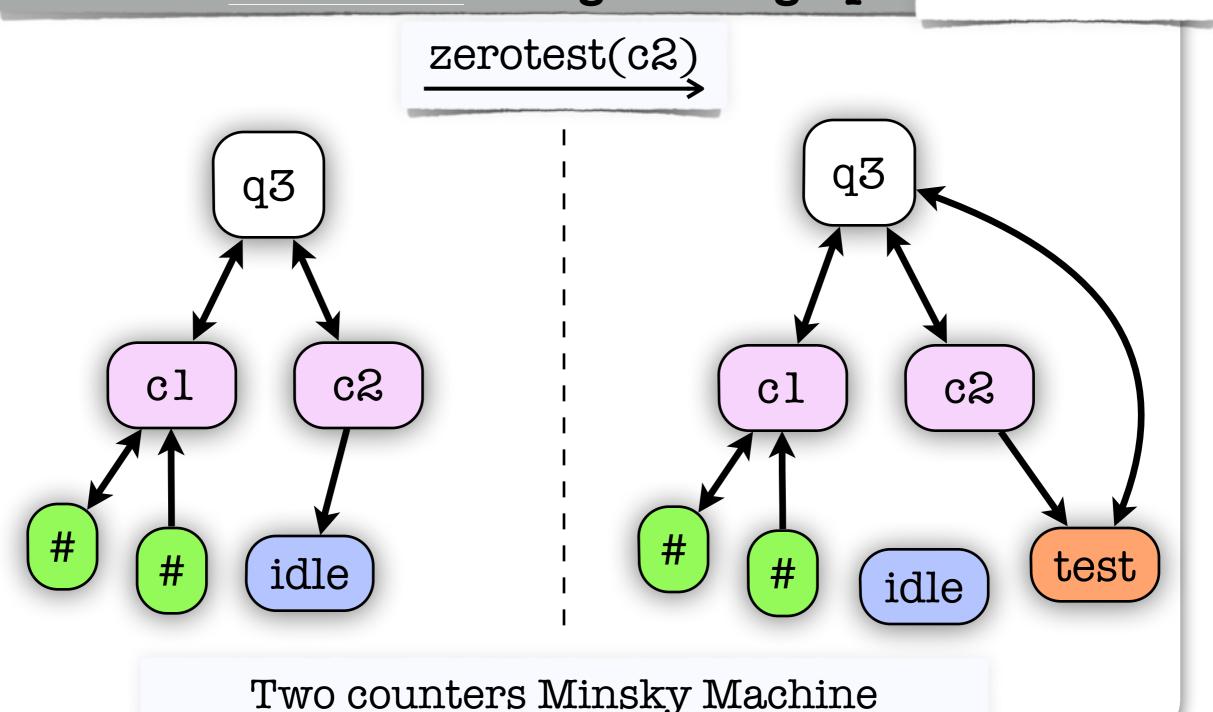

Two counters Minsky Machine

100

10

Verification of Dynamic Register Automata

# Bound the Simple Path Length of the underlying undirected configuration graph Undecidable

Two counters Minsky Machine

Strongly-Bounded Reachability

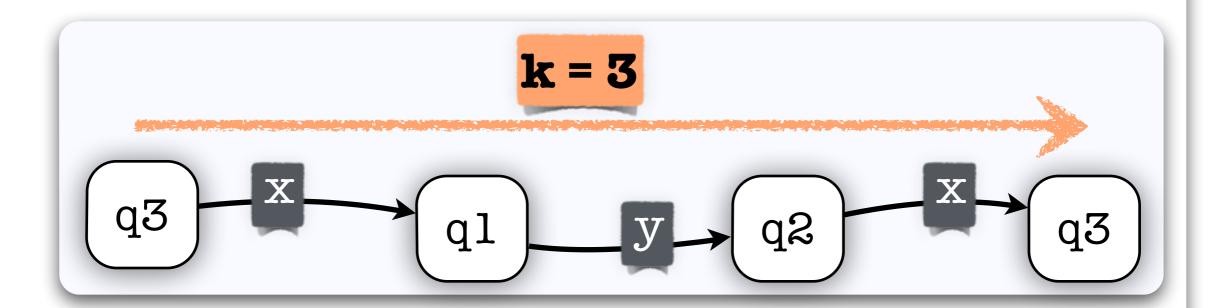

### Strongly Bounded DRA

Verification of Dynamic Register Automata

# Bound the Simple Path Length of the underlying undirected configuration graph Undecidable

Two counters Minsky Machine

k = 4 Strongly-Bounded Reachability

Bound the Simple Path Length of the underlying undirected configuration graph Undecidable

Two counters Minsky Machine

### Strongly Bounded DRA

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

100

Verification of Dynamic Register Automata

### Strongly Bounded DRA

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Bound the Simple Path Length of the underlying undirected configuration graph Undecidable

Two counters Minsky Machine

### Strongly Bounded DRA

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

### State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

**Decidable**

Verification of Dynamic Register Automata

State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

**Decidable**

Verification of Dynamic Register Automata

State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

Degenerative DRA

**Decidable**

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

Verification of Dynamic Register Automata

State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

Degenerative DRA

Decidable

Verification of Dynamic Register Automata

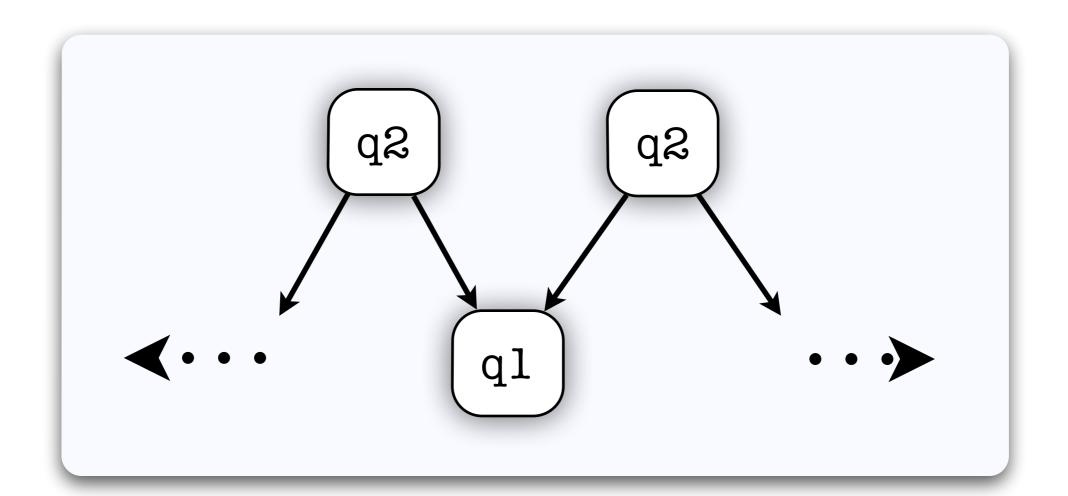

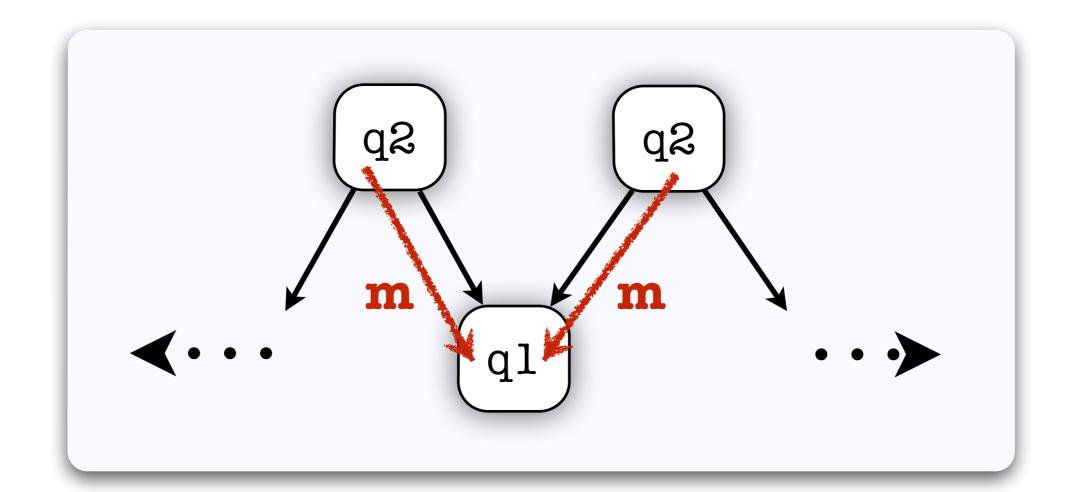

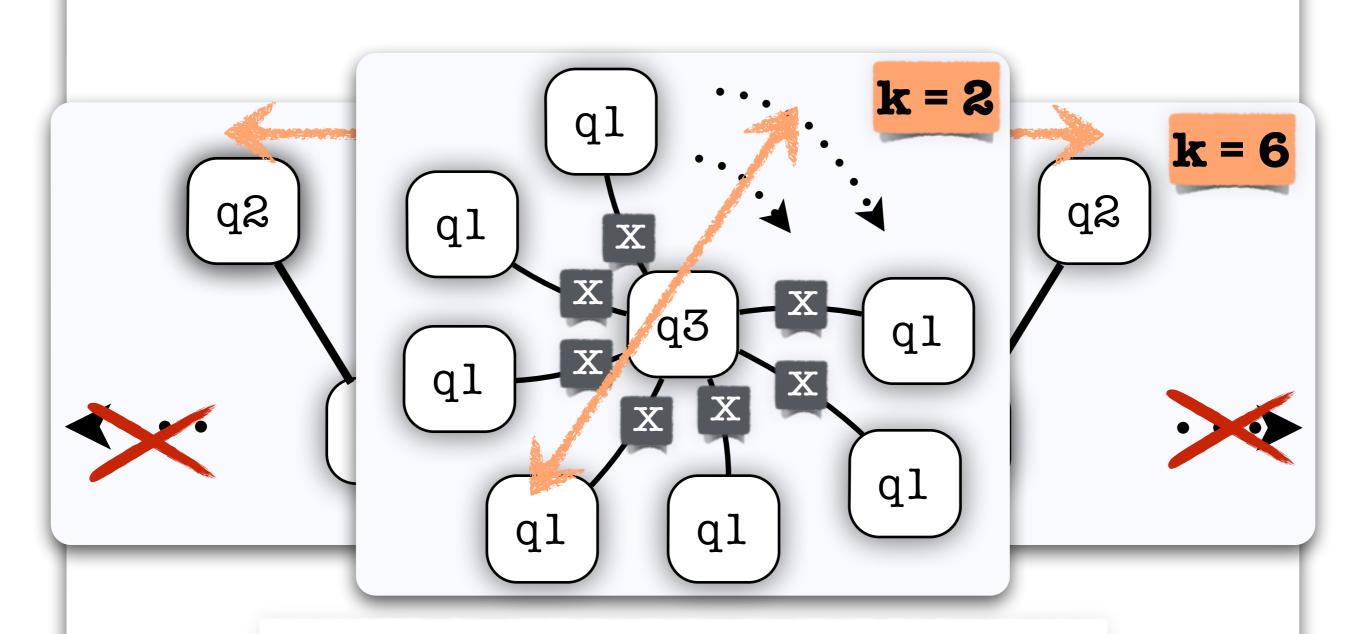

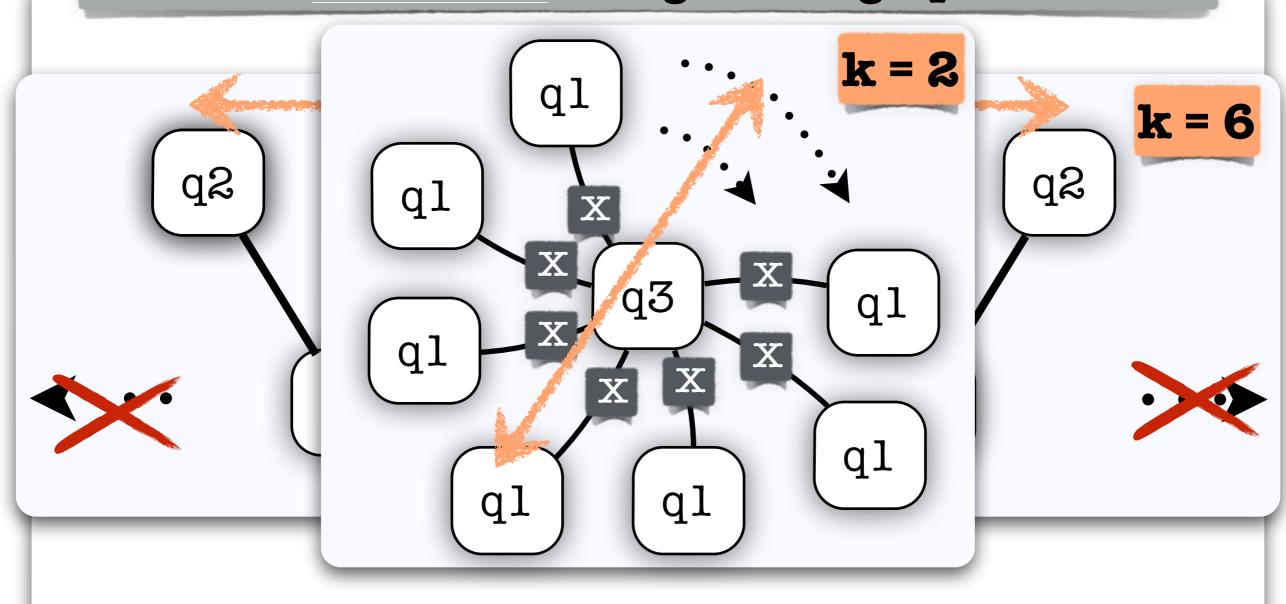

#### DRA is degenerative

Verification of Dynamic Register Automata

#### DRA is degenerative

Bound the Simple Path Length of the underlying undirected configuration graph

#### **Well-Structured Transition Systems**

[Abdulla et al. 1996], [Finkel et al. 2001]

Symbolic representation of infinite set of configurations

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

- Define a Well-Quasi Order on configurations

- ▶ Prove **Monotonicity** of Transition Relation

- Provide an algorithm to compute the **Pre** of an upward closed set

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

- Define a Well-Quasi Order on configurations

- ▶ Prove **Monotonicity** of Transition Relation

- Provide an algorithm to compute the **Pre** of an upward closed set

Verification of Dynamic Register Automata

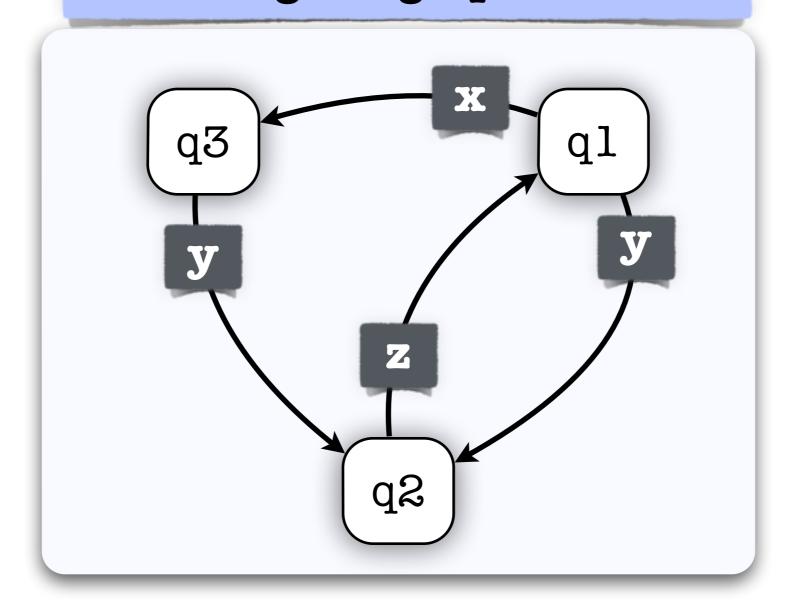

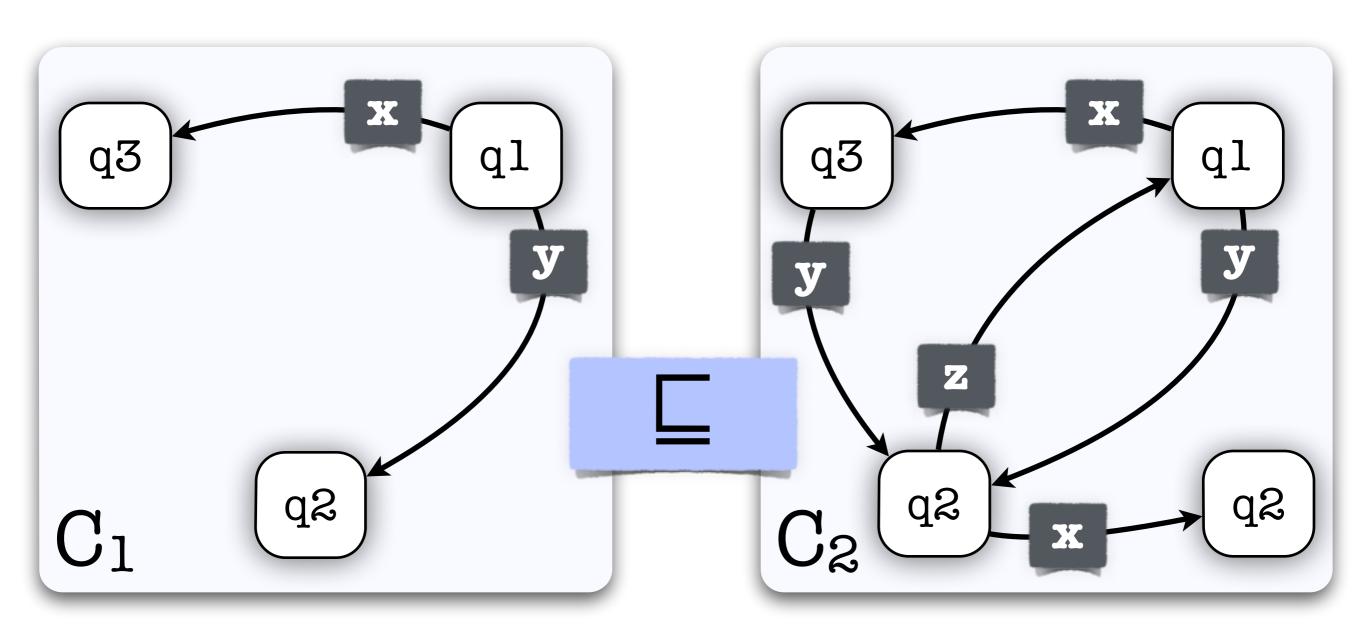

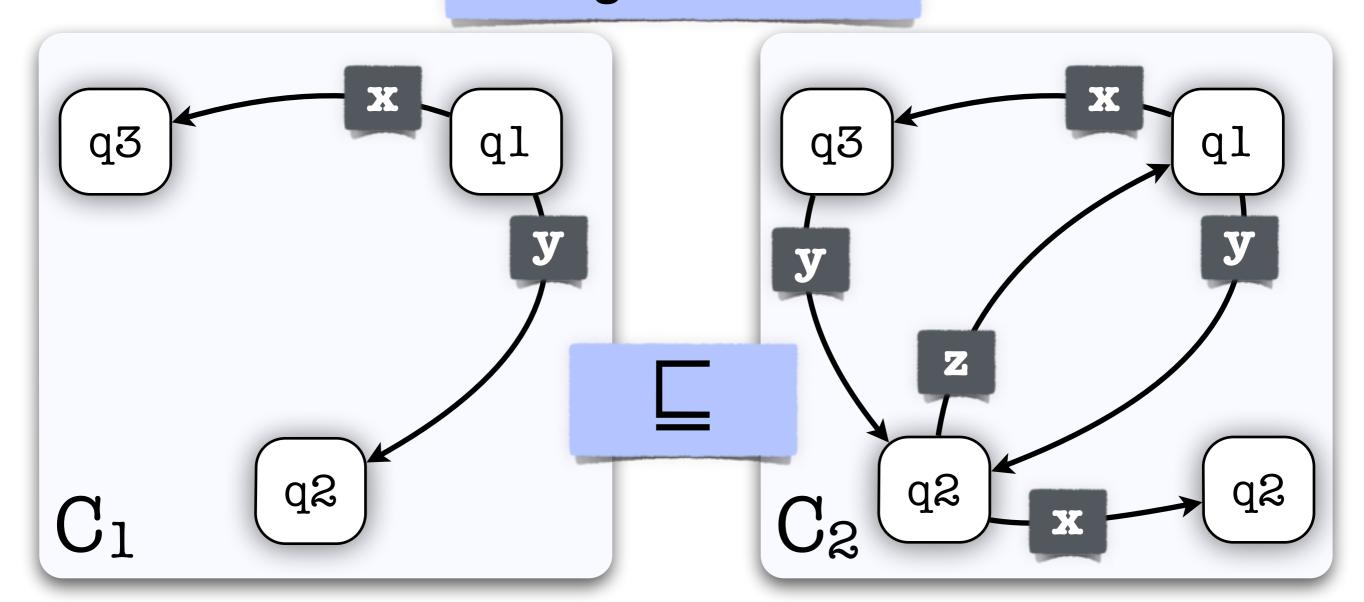

#### **Well-Structured Transition Systems**

Define a Well-Quasi Order on configurations

#### Ordering: subgraph relation

Verification of Dynamic Register Automata

#### Well-Structured Transition Systems

Define a Well-Quasi Order on configurations

#### Ordering: subgraph relation

Verification of Dynamic Register Automata

#### Well-Structured Transition Systems

Define a Well-Quasi Order on configurations

Ordering: subgraph relation

[Ding, 1992] Subgraphs and Well-Quasi Ordering

(Induced) subgraph relation is a WQO on Strongly-Bounded graphs

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Define a Well-Quasi Order on configurations

#### Ordering: subgraph relation

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Define a Well-Quasi Order on configurations

#### Ordering: subgraph relation

Verification of Dynamic Register Automata

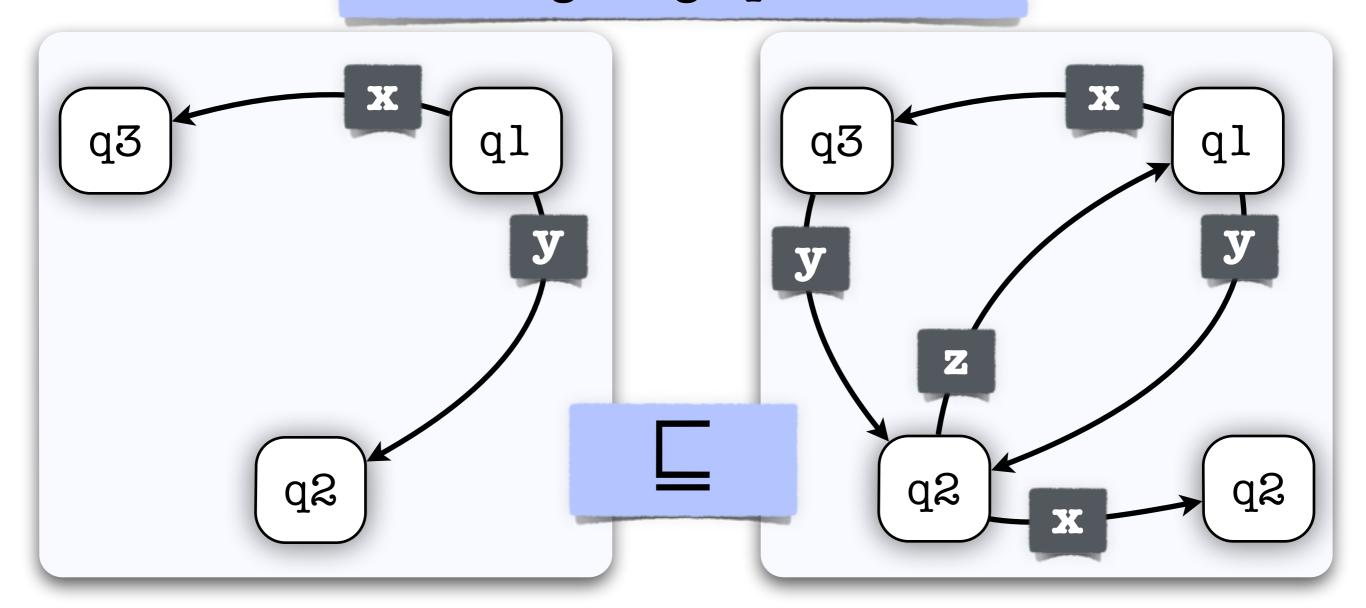

#### **Well-Structured Transition Systems**

- Define a Well-Quasi Order on configurations

- ▶ Prove **Monotonicity** of Transition Relation

- Provide an algorithm to compute the **Pre** of an upward closed set

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

- Define a Well-Quasi Order on configurations

- ▶ Prove **Monotonicity** of Transition Relation

- Provide an algorithm to compute the **Pre** of an upward closed set

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

▶ Prove **Monotonicity** of Transition Relation

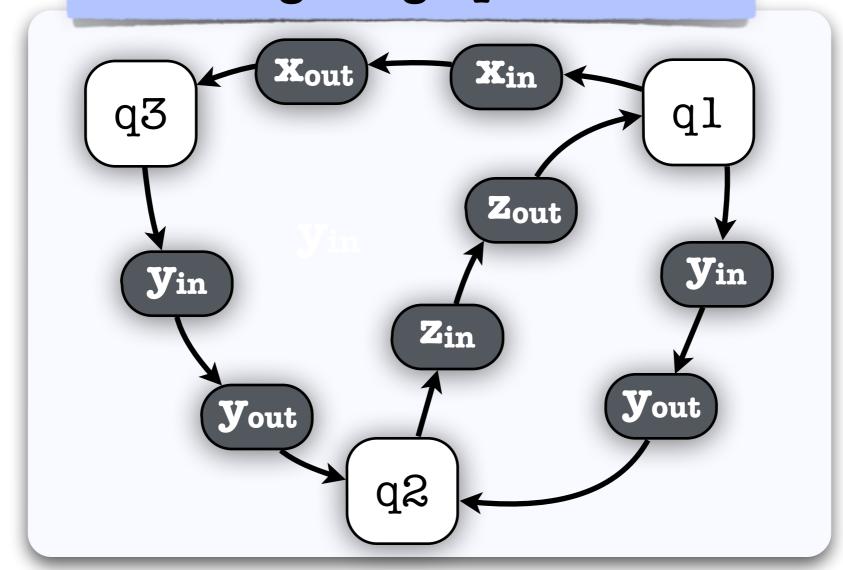

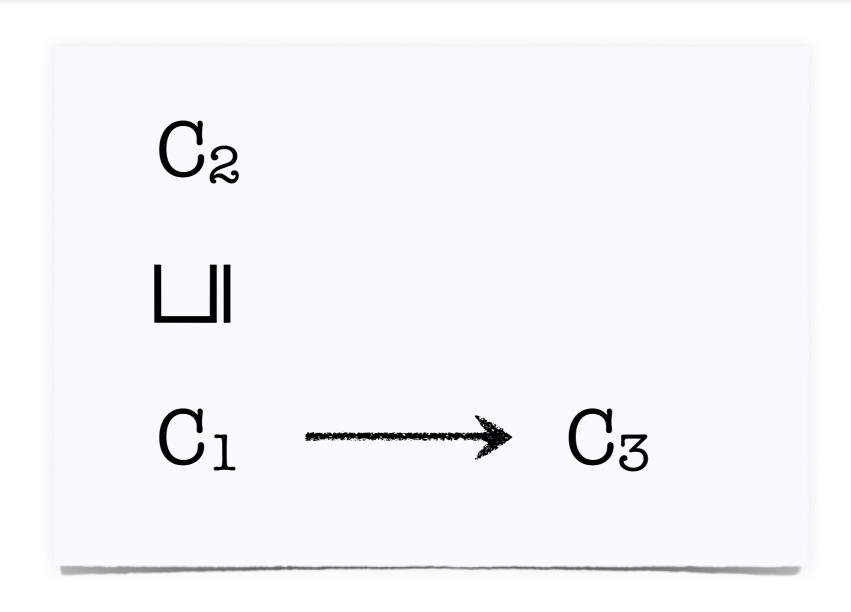

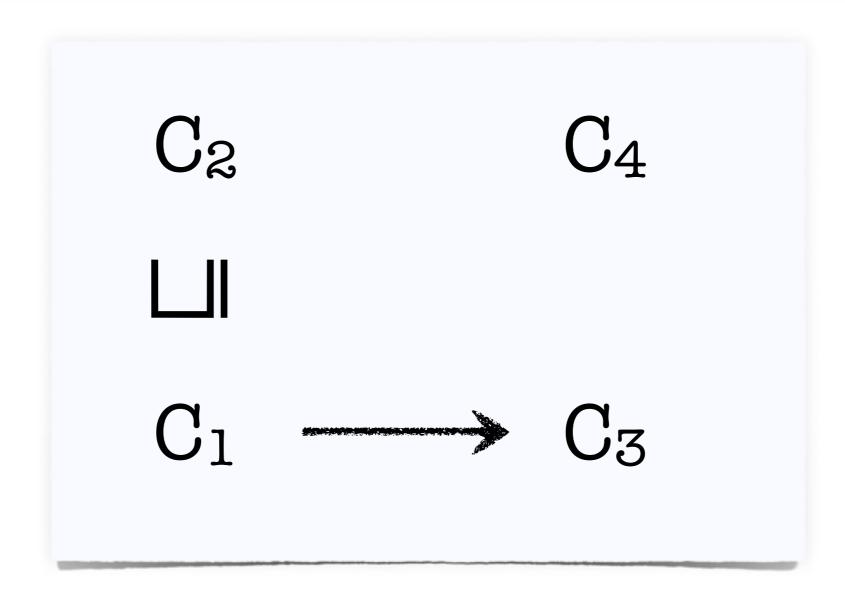

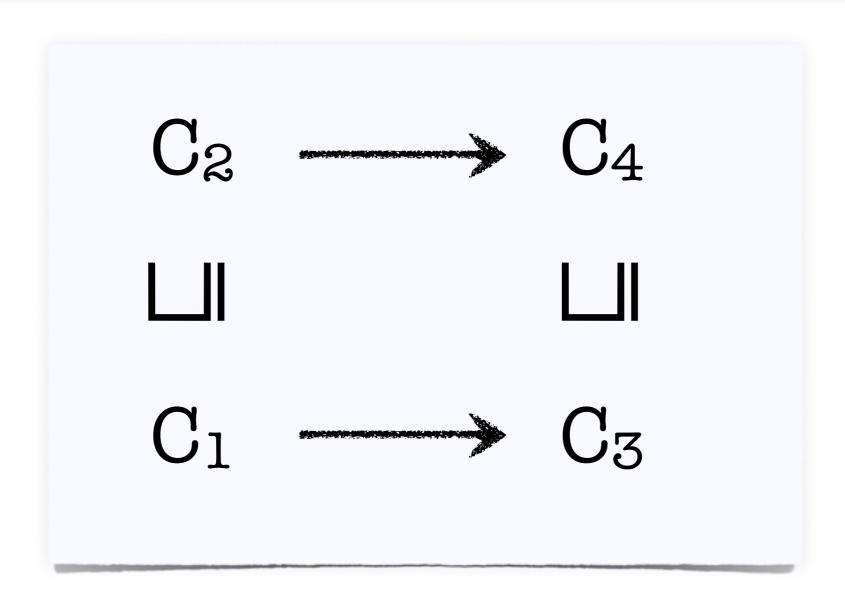

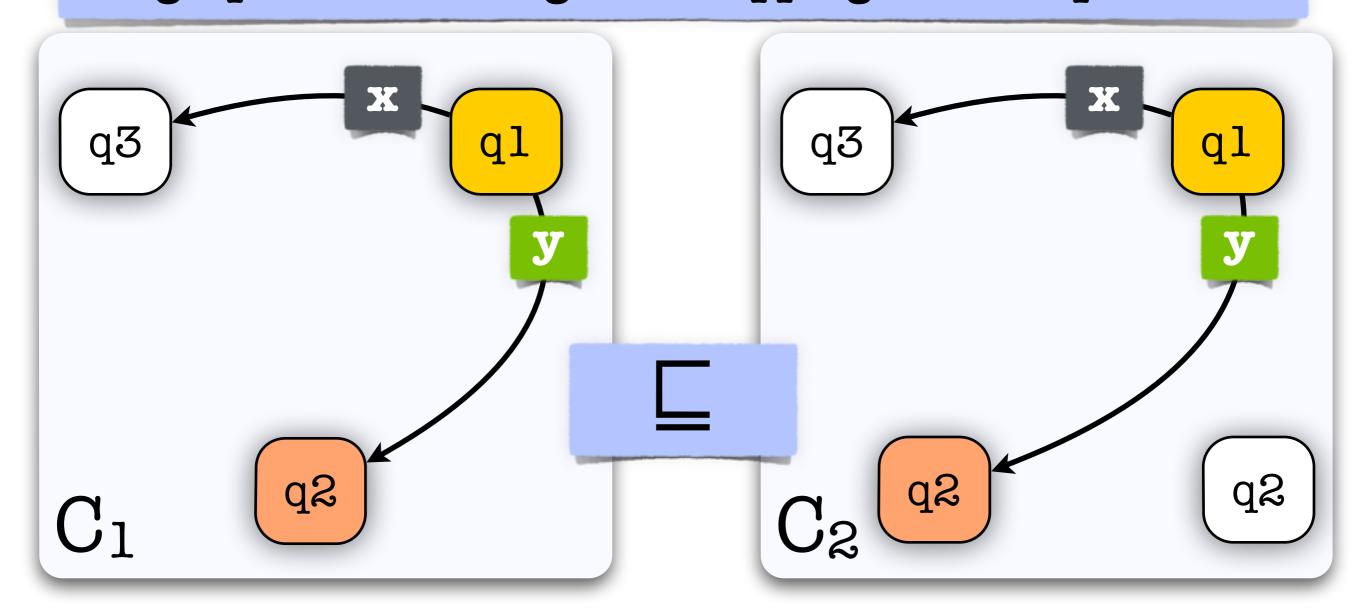

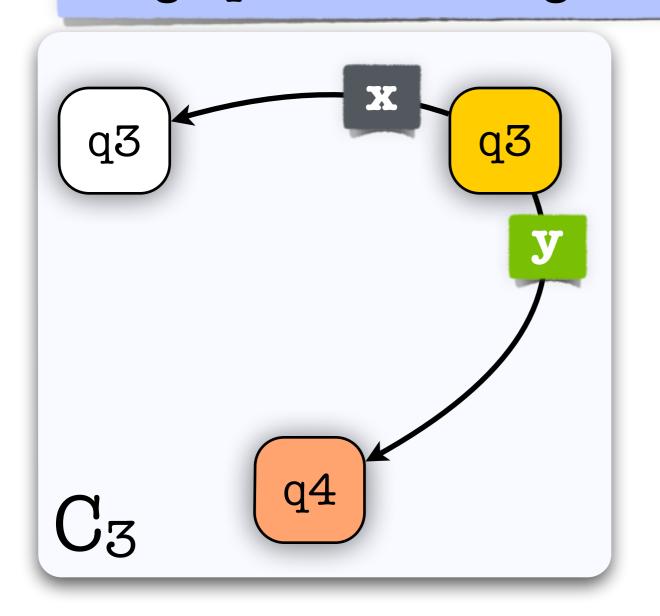

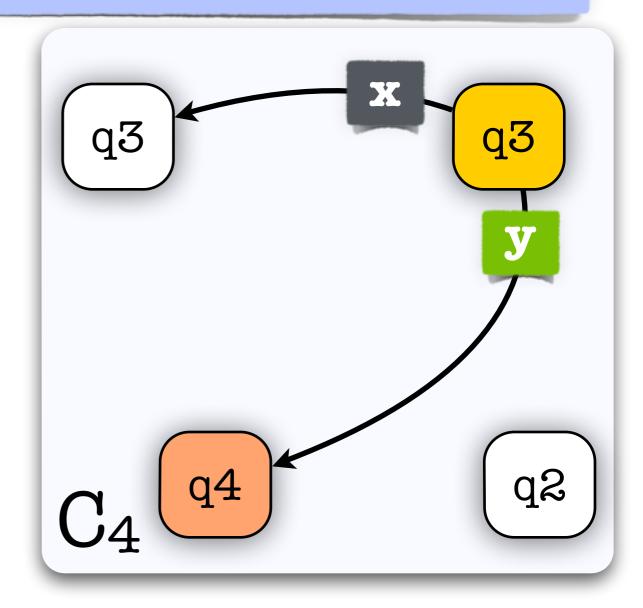

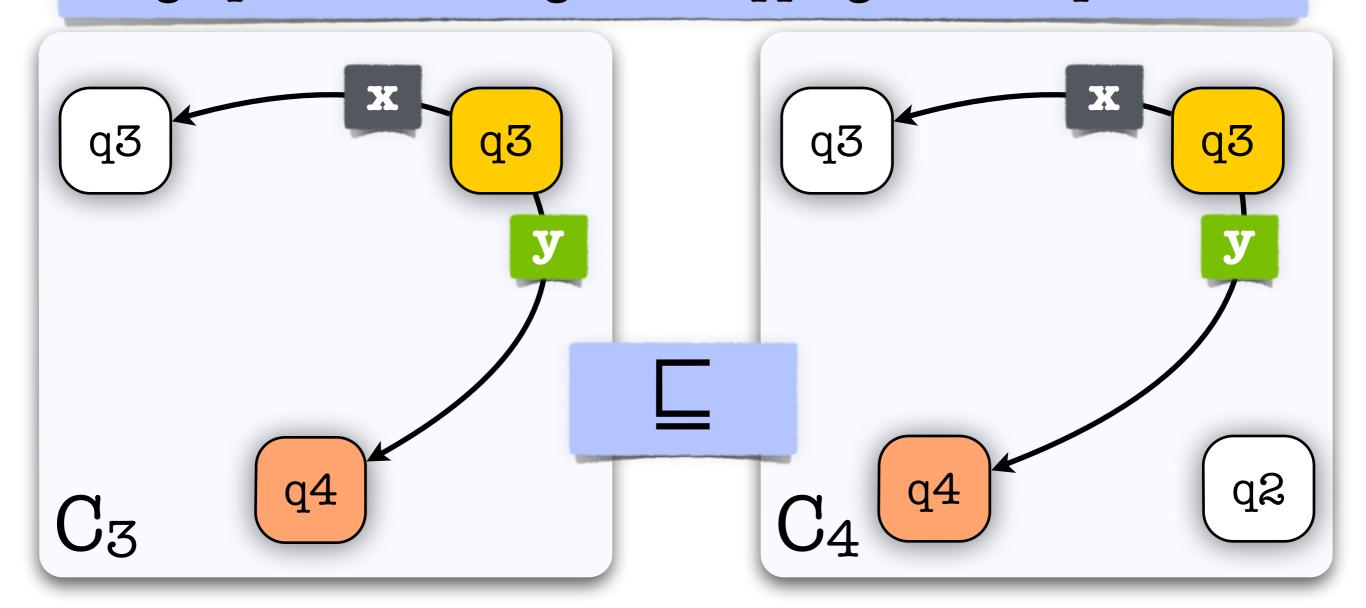

$C_2$  $C_1$  $C_3$  Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

▶ Prove **Monotonicity** of Transition Relation

Ca  $C_1$  $C_3$  128

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

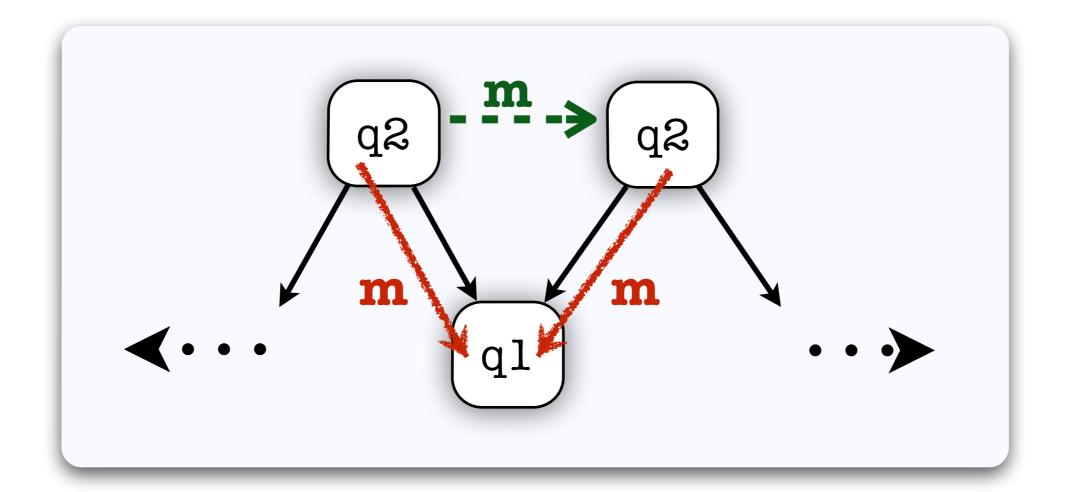

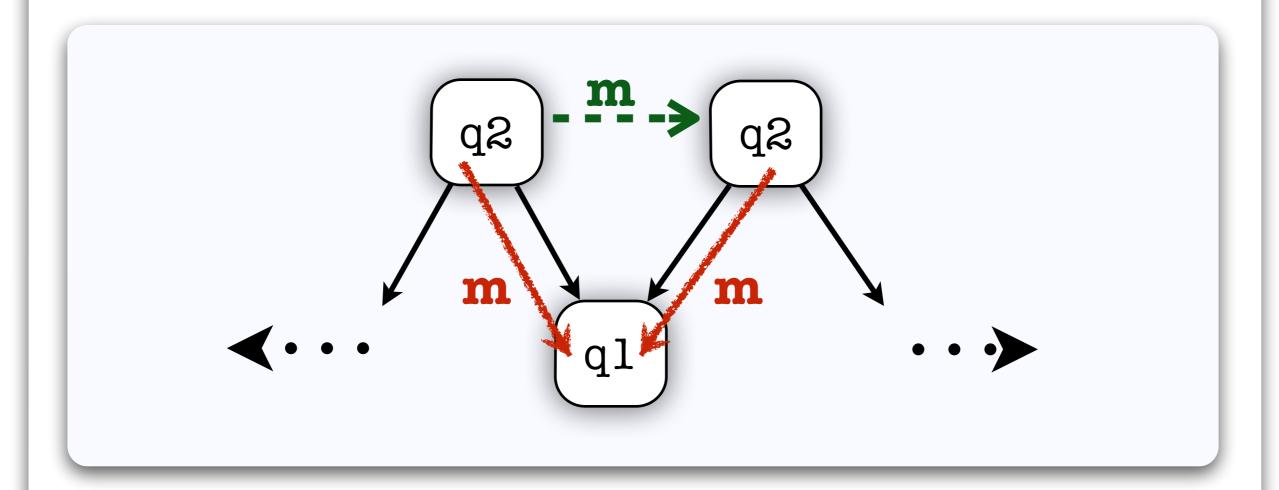

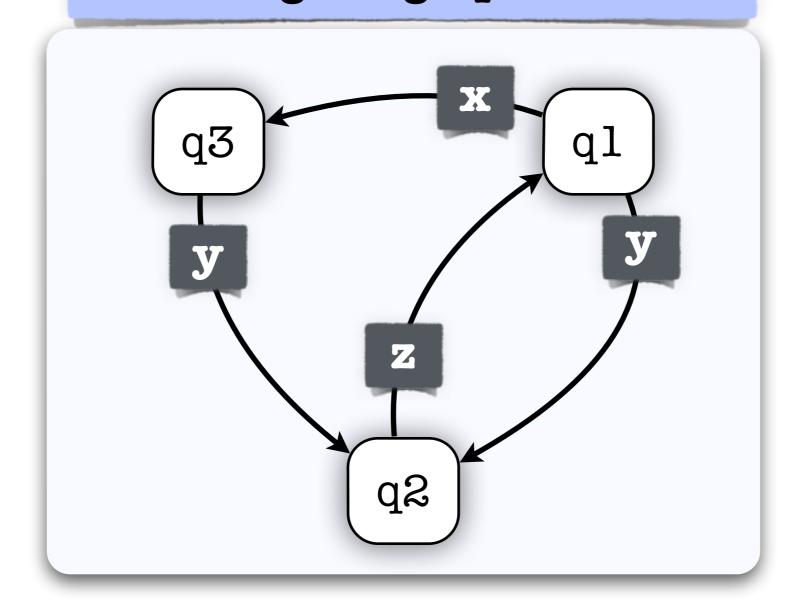

▶ Prove **Monotonicity** of Transition Relation

#### Degenerative

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

▶ Prove **Monotonicity** of Transition Relation

#### Degenerative

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

Verification of Dynamic Register Automata

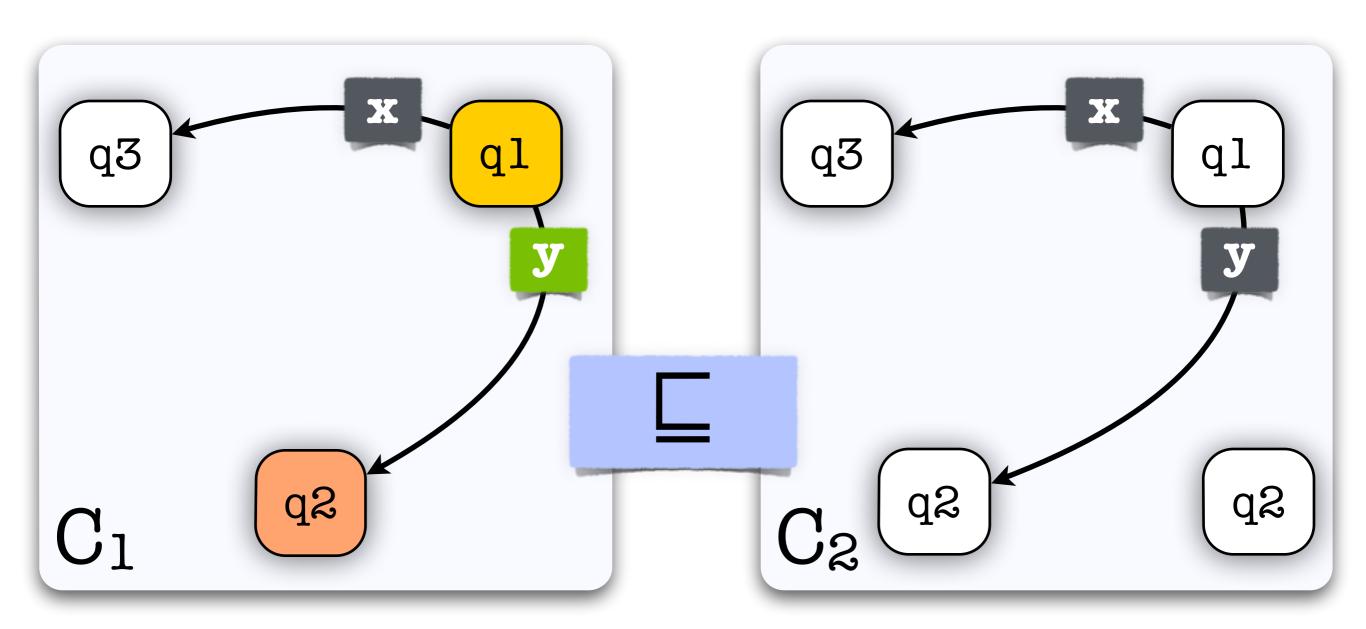

#### Well-Structured Transition Systems

▶ Prove **Monotonicity** of Transition Relation

Subgraph relation: Register Mapping & States preserved

Verification of Dynamic Register Automata

#### Well-Structured Transition Systems

▶ Prove **Monotonicity** of Transition Relation

#### Subgraph relation: Register Mapping & States preserved

Verification of Dynamic Register Automata

#### Well-Structured Transition Systems

▶ Prove **Monotonicity** of Transition Relation

Subgraph relation: Register Mapping & States preserved

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

- Define a Well-Quasi Order on configurations

- ▶ Prove **Monotonicity** of Transition Relation

- Provide an algorithm to compute the **Pre** of an upward closed set

Verification of Dynamic Register Automata

#### **Well-Structured Transition Systems**

- Define a Well-Quasi Order on configurations

- ▶ Prove **Monotonicity** of Transition Relation

- Provide an algorithm to compute the **Pre** of an upward closed set

14

Verification of Dynamic Register Automata

### State Reachability

**Bounded DRA**

Undecidable

Strongly Bounded DRA

Undecidable

Strongly Safe DRA

Degenerative DRA

**Decidable**

### Conclusion

Verification of Dynamic Register Automata

### Dynamic Register Automata

**Dynamic Creation of Processes**

Register Mapping

Point-to-Point Comm.

Rendez-Vous Comm.

### State Reachability

**Bounded DRA**

Strongly Bounded DRA

Strongly Safe DRA

Undecidable

Undecidable

Decidable